2 nvidia® tegra™ 250, 3 system dram, 4 boot device – Nvidia TEGRA DG-04927-001_V01 User Manual

Page 8

Tegra 200 Series Developer Board User Guide

DG-04927-001_v01

Advance Information – Subject to Change

8

NVIDIA CONFIDENTIAL

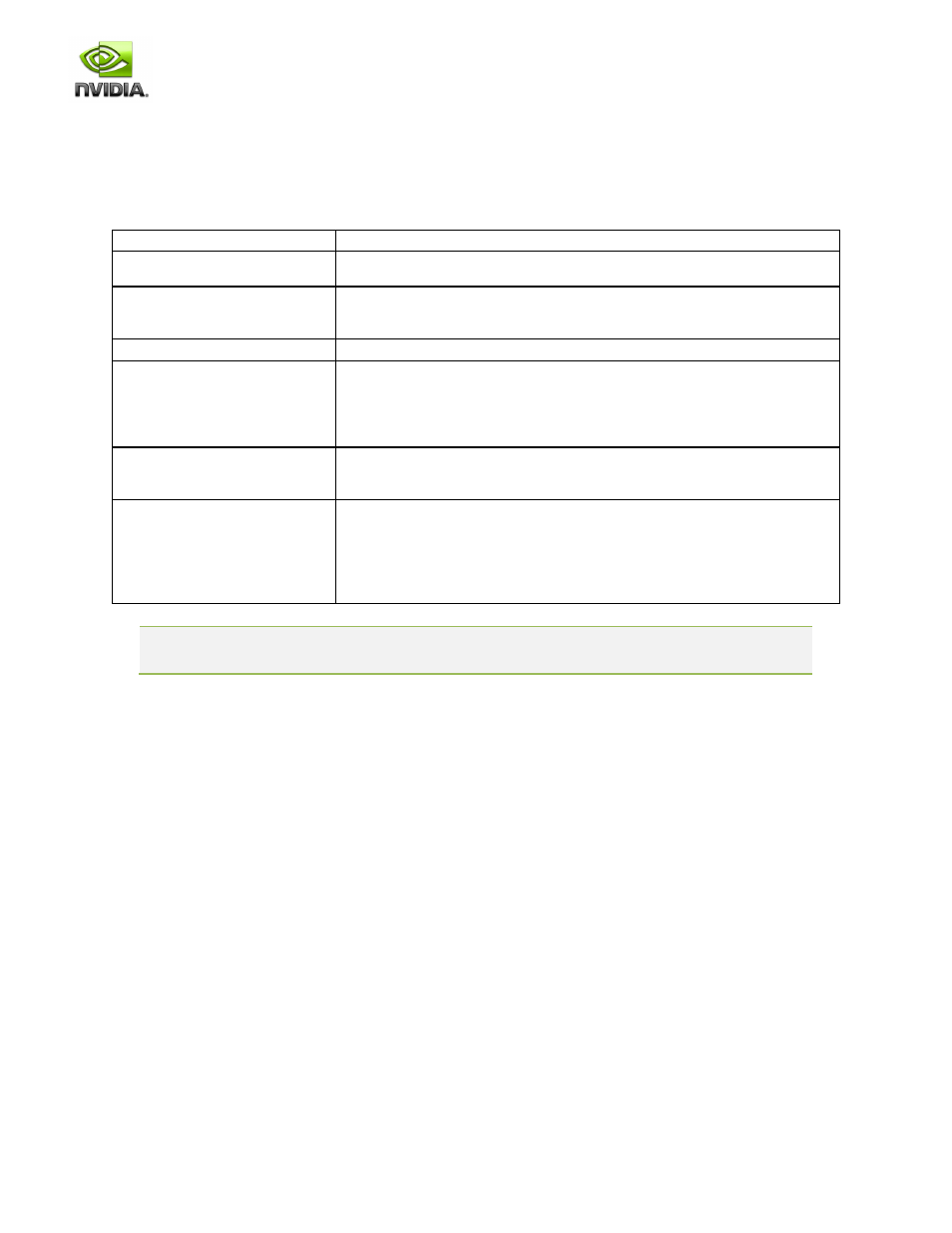

2.2 NVIDIA® Tegra™ 250

The NVIDIA Tegra 250 computer-on-a-chip is suited for handheld and mobile applications. It’s primary purpose is to control all

system peripherals and provide computing power.

Table 1 Features (Available / Used on Tegra 200 Series Developer Board)

CPU

Dual-core ARM® Cortex-A9 MPCore™ processor

External Memory Support

32-bit 333MHz DDR2 SDRAM (to 1GB)

2 chip selects

Advanced Power Management

Dynamic voltage and frequency scaling

Multiple clock and power domains

Independent gating of power domains

2D/3D acceleration

Integrated Open GLES 2.0 3D core

Connectivity and Expansion

SPI (Qty 1), I2C (Qty 3), UART (Qty 2)

I2S/PCM (Qty 2)

ULPI HS

USB 2.0 HS (Qty 3)

SDIO (Qty 3)

Storage

Internal 4-bit SD/8-bit MMC

o eMMC compatible module available

External 4-bit MMC/SD

Multimedia Support

Dual Display (Integrated LCD + external)

18-bit LVDS LCD

HDMI to 1080p and VGA

Camera (CSI)

Pre/Post Processing Acceleration with ISP

MPEG-4/H264/JPEG Encoder

Note:

For more information on Tegra 250, refer to the Tegra 200 Series Datasheet (Electrical, Mechanical and

Thermal Specifications and the Design Guide.

2.3 System DRAM

The Tegra 200 Series Developer Board has 8 DDR2 128M x 8 devices for 1GB total system DRAM. The DDR2 will operate up

to 333MHz for a peak bandwidth of 2.7GB/s. The memory is arranged as one or two 32-bit Ranks. Each Rank uses a different

Chip Select and Clock Enable. For low power operation with memory retention, self refresh is supported.

2.4 Boot Device

A 4Gb (512MB) Hynix HY27UF084G2BTPCB 8-bit NAND is available for use as the boot device. In addition, an internal 4-bit

SD, 8-bit MMC socket (J26) is provided to support other flash memories.