2 power supplies – Nvidia TEGRA DG-04927-001_V01 User Manual

Page 17

Tegra 200 Series Developer Board User Guide

DG-04927-001_v01

Advance Information – Subject to Change

17

NVIDIA CONFIDENTIAL

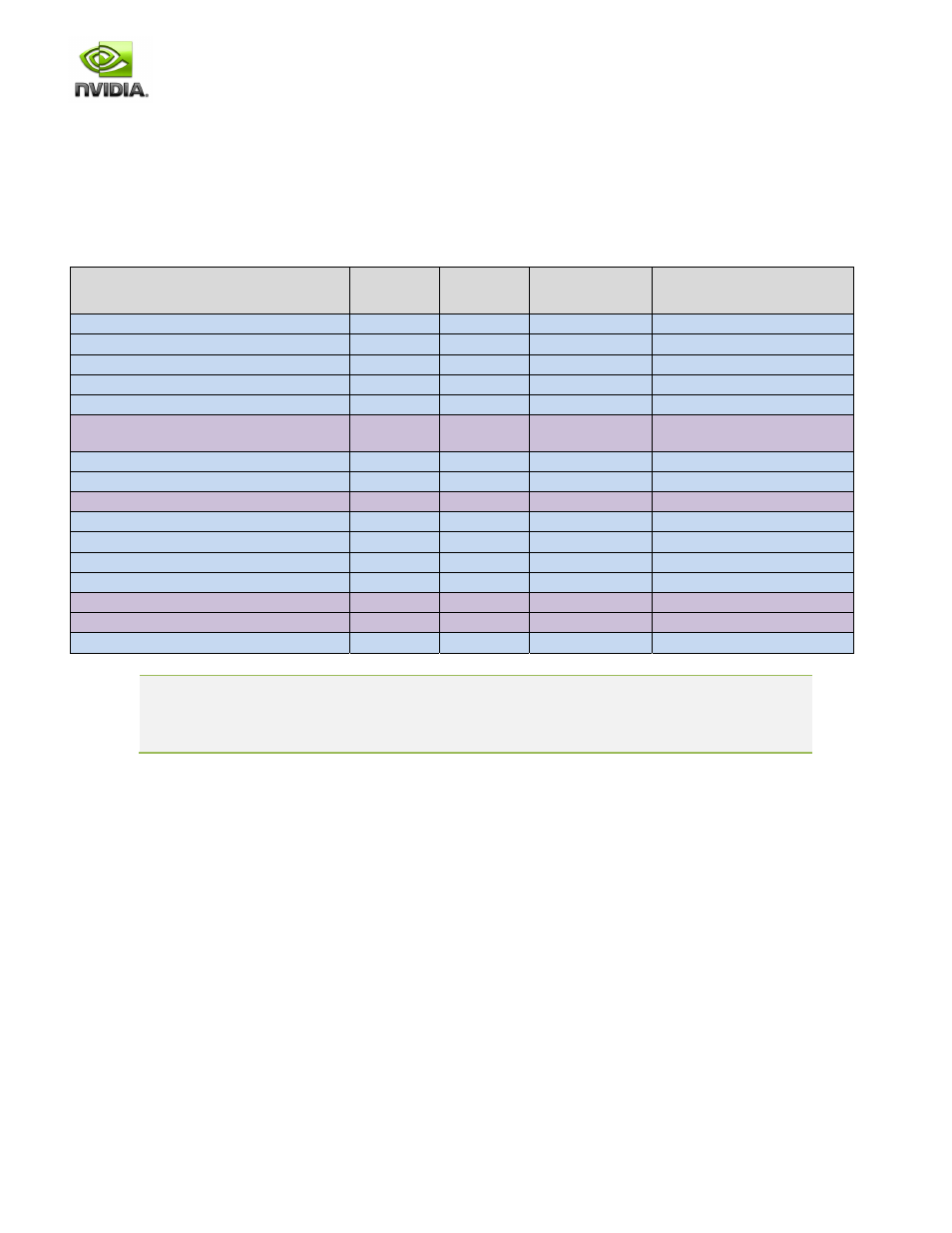

4.1.2 Power Supplies

The Tegra 250 has 29 power rails (3 cores, 14 analog and 12 digital I/O). Depending on system design, many of the rails can

share a power supply, and some are not needed for all designs. The example shown in Table 4 is based on the Smartbook

Development System design and should be representative of these types of designs. This table mainly lists the supplies

required by the Tegra 250. Others are required to support some of the peripherals typically seen in a Smartbook.

Table 4 Tegra 250 Power Supply Allocation Example

Power Rails

Supported

Voltages (V)

Voltage (V)

(Tegra 200

Series DB)

Power Supply

Enable

VDD_RTC

1.0 – 1.2

Up to 1.2

PMU LDO2

PMU SM2 (3.7V) + Internal Trigger

VDD_CORE

1.0 – 1.2

Up to 1.2

PMU SM0

CORE_PWR_REQ + Internal Trigger

VDD_CPU

0.9 – 1.0

Up to 1.0

PMU SM0

CPU_PWR_REQ + Internal Trigger

AVDD_PLLx

1.1

1.1

PMU LDO1

PMU SM2 (3.7V) + Internal Trigger

VDDIO_SYS, AVDD_OSC

1.8

1.8

PMU LD04

PMU SM2 (3.7V) + Internal Trigger

VDDIO_LCD,VDDIO_BB,VDDIO_AUDIO,VDDIO_UART

VDDIO_DDR

1.8,2.8,3.3

1.8

1.8

TPS51116, DC/DC

EN_VDD_1V8

(PG_VDDIO_SYS – PMU LDO4PG)

AVDD_USB, AVDD_USB_PLL

3.3

3.3

PMU LDO3

PMU SM2 (3.7V) + Internal Trigger

VDD_DDR_RX

2.8

2.8

PMU LDO9

PMU SM2 (3.7V) + Internal Trigger

VDDIO_NAND (if 3.3V), VDDIO_SDIO, VDDIO_VI

1.8,2.8,3.3

3.3

TPS51220, DC/DC

EN_VDD_3V3 (Output of SR)

AVDD_VDAC

2.7 – 3.3

2.85

PMU LDO6

PMU SM2 (3.7V)

AVDD_HDMI

3.3

3.3

PMU LDO7

PMU SM2 (3.7V)

AVDD_HDMI_PLL

1.8, 2.5

1.8

PMU LDO8

PMU SM2 (3.7V)

VDDIO_PEX_CLK

3.3

3.3

PMU LDO0

PMU SM2 (3.7V)

AVDD_DSI_CSI

1.2

1.2

TPS72012, LDO2

EN_VDD_1V2 (PMU GPIO)

AVDD_PCIE, AVDD_PEX, AVDD_PEX_PLL, VDD_PEX

1.05

1.05

TPS62290, DC/DC

EN_VDD_1V05 (PMU GPIO)

VCORE_MMC

2.7 – 3.6

2.85

PMU LD05

Note:

1: This includes pins AVDD_PLLA_C_P (powers PLLA, PLLC and PLLP), AVDD_PLLM, AVDD_PLLU (powers

PLLU and PLLD) and AVDD_PLLX. If PCIE not supported in a design, AVDD_PCIE should be left

unpowered as the leakage is significant.

2: Supplies must meet maximum rate requirement in AP20 EMT of 165mV/us