Design considerations – National Instruments HPC167064 User Manual

Page 25

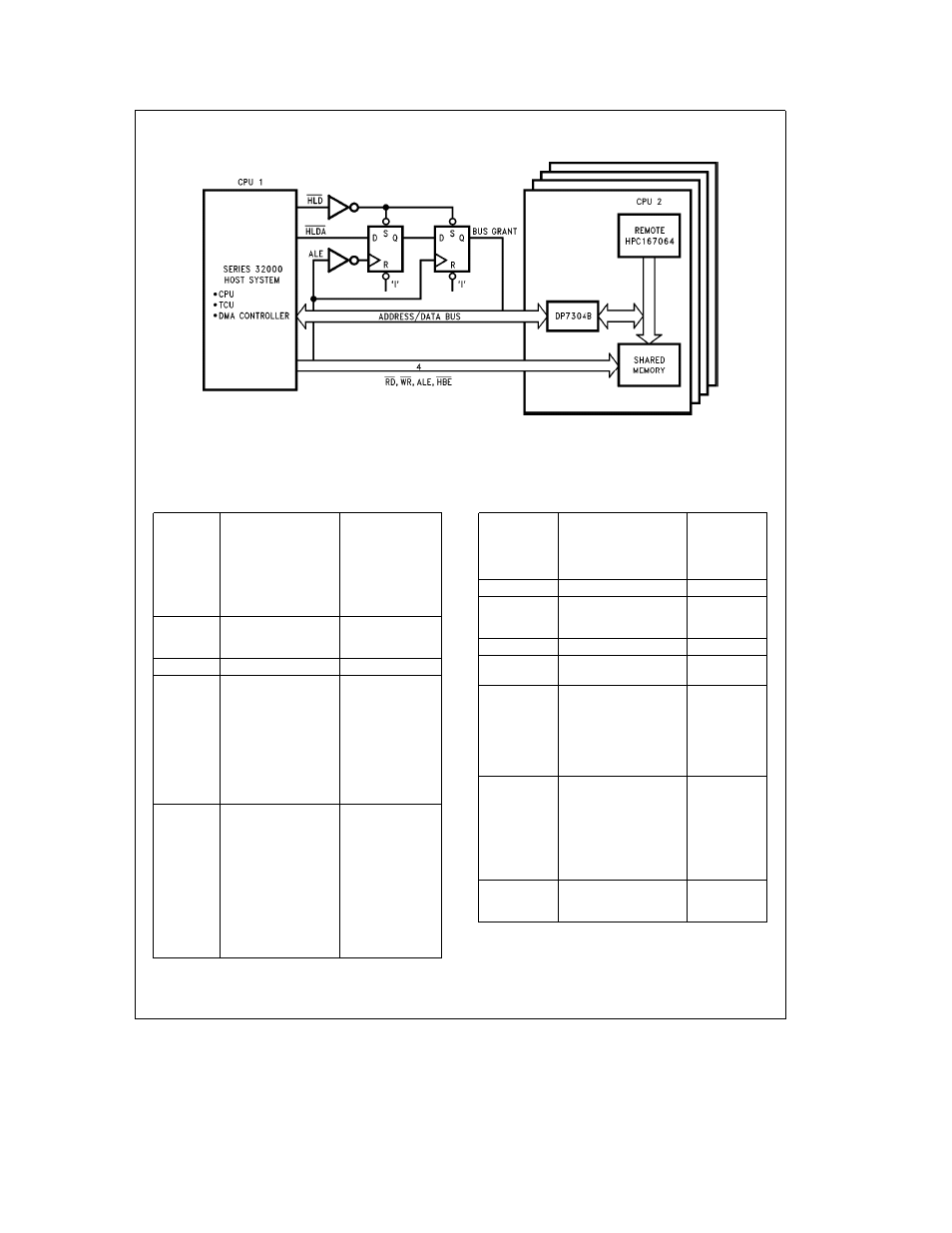

Shared Memory Support

(Continued)

TL DD 11046 – 36

FIGURE 28 Shared Memory Application (HPC167064 Interface to Series 32000 System)

Design Considerations

TABLE III Memory Map of HPC167064 Emulating an HPC16064

FFFF FFF0

Interrupt Vectors

FFEF FFD0

JSRP Vectors

FFCF FFCE

On-Chip ROM

User Memory

C001 C000

(

BFFF BFFE

External Expansion

Memory

0301 0300

(

02FF 02FE

On-Chip RAM

User RAM

01C1 01C0

(

0195 0194

WATCHDOG Register

WATCHDOG Logic

0192

T0CON Register

0191 0190

TMMODE Register

018F 018

DIVBY Register

018D 018C

T3 Timer

018B 018A

R3 Register

Timer Block T0 T3

0189 0188

T2 Timer

0187 0186

R2 Register

0185 0184

I2CR Register R1

0183 0182

I3CR Register T1

0181 0180

I4CR Register

015E 015F

EICR

015C

EICON

0153 0152

Port P Register

0151 0150

PWMODE Register

014F 014E

R7 Register

014D 014C

T7 Timer

014B 014A

R6 Register

Timer Block T4 T7

0149 0148

T6 Timer

0147 0146

R5 Register

0145 0144

T5 Timer

0143 0142

R4 Register

0141 0140

T4 Timer

0128

ENUR Register

0126

TBUF Register

0124

RBUF Register

UART

0122

ENUI Register

0120

ENU Register

0104

Port D Input Register

00F5 00F4

BFUN Register

Ports A

B

00F3 00F2

DIR B Register

Control

00F1 00F0

DIR A Register IBUF

00E6

UPIC Register

UPI Control

00E3 00E2

Port B

Ports A

B

00E1 00E0

Port A OBUF

00DE

Reserved

00DD 00DC

HALT Enable Register

Port Control

00D8

Port I Input Register

Interrupt

00D6

SIO Register

Control

00D4

IRCD Register

Registers

00D2

IRPD Register

00D0

ENIR Register

00CF 00CE

X Register

00CD 00CC

B Register

00CB 00CA

K Register

00C9 00C8

A Register

HPC Core

00C7 00C6

PC Register

Registers

00C5 00C4

SP Register

00C3 00C2

Reserved

00C0

PSW Register

00BF 00BE

On-Chip

RAM

User RAM

0001 0000

25