Power-on reset (por), Voltage-low detector, Nxp semiconductors – NXP Semiconductors UM10301 PCF2123 User Manual

Page 8

NXP Semiconductors

UM10301

User Manual PCF85x3, PCA8565 and PCF2123, PCA2125

UM10301_1

© NXP B.V. 2008. All rights reserved.

User manual

Rev. 01 — 23 December 2008

8 of 52

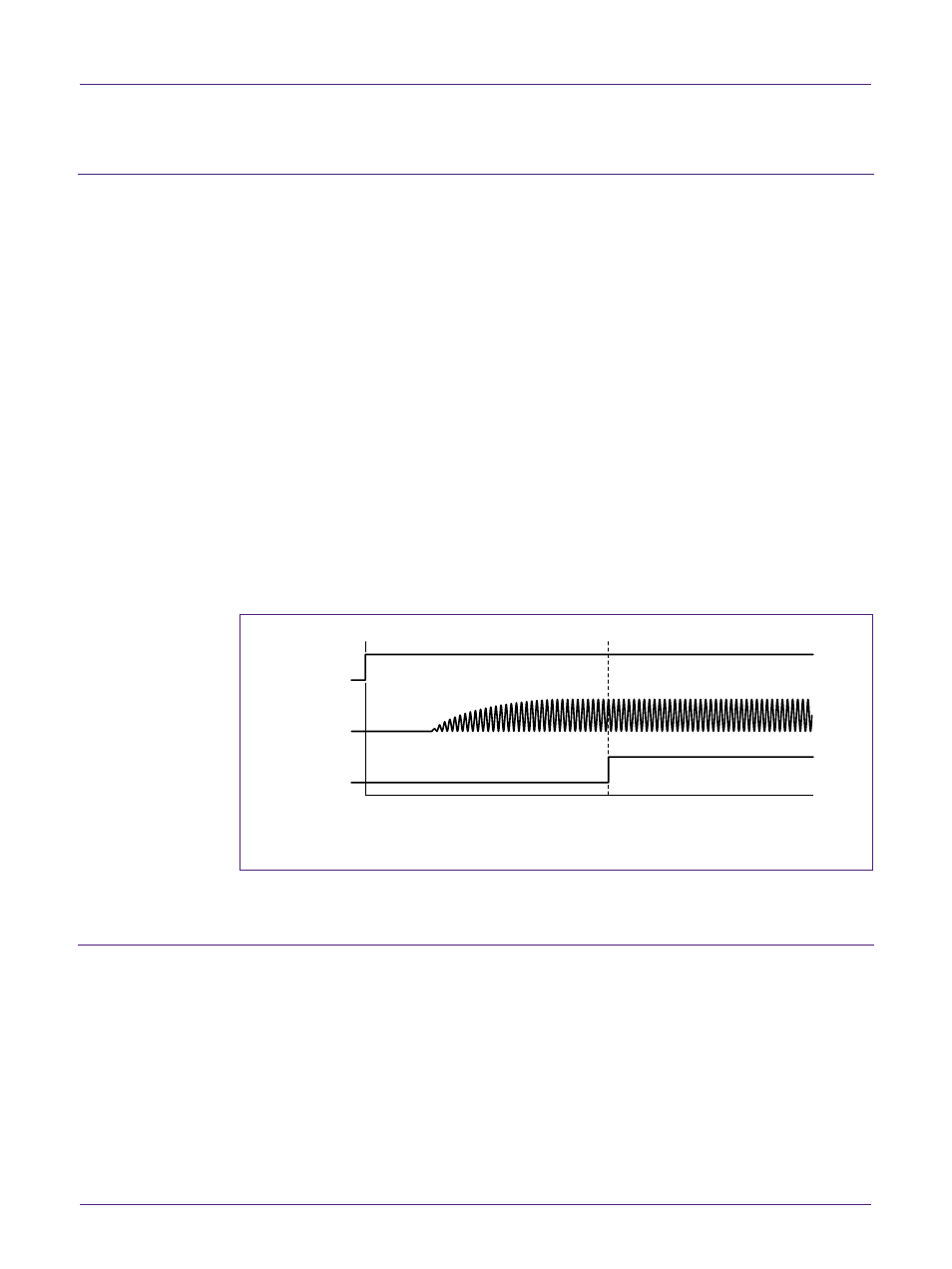

4. Power-on reset (POR)

Traditionally a power-on reset circuit is a circuit that generates a reset pulse once the

supply voltage has reached a certain value upon power-up. The purpose is to ensure a

defined behavior at start-up. This type of power-on reset is not present in these RTCs.

The power-on reset circuit (POR) for these RTCs does not look at the supply voltage, but

instead it is based on an internal reset circuit which is active whenever the oscillator is

stopped, refer to Fig 1. When power is applied to the device it will take some time for the

oscillator to start and during this time the circuit will generate a reset. Also when during

operation the OSCI- or OSCO-pin is pulled to ground, causing oscillation to stop, the

POR will generate a reset pulse. In the reset state the serial bus logic is initialized and all

registers are reset according to the register reset values. Not all registers will be reset.

The only registers that are reset are the ones that control a function i.e. decide on clock

mode, enable an alarm etc. Refer to the datasheet of the respective device for details.

The power on reset duration is thus directly related to the crystal oscillator start-up time.

Due to the long start-up times experienced by these types of circuits on-board testing of

the device would take longer too. In order to speed up this, a mechanism has been built

in to disable the POR (not for PCF8583, PCF8593 and PCF2123). This is called Power-

on reset override. Again, refer to the respective datasheet for details. Once the override

mode has been entered, the device stops immediately being reset and set-up operation

e.g. entry into the external clock test mode, may commence via the serial interface.

001aaf897

chip in reset

chip not in reset

t

V

DD

oscillation

internal

reset

Fig 1. Power-on reset

5. Voltage-low

detector

PCF8563, PCA8565 and PCF2123 have an on-chip voltage-low detector, see Fig 2 and

Fig 3. When V

DD

drops below a certain limit defined as V

low

, bit VL in the seconds register

of PCF8563 and PCA8565 is set. Generally the VL-bit is intended to indicate that the

time might be wrong, not that it necessarely is wrong. It will be set if one of the following

four conditions occur:

• The power has just been applied;

• The power has dipped down and then recovered;

• The power has gone away and then come back again;

• When the oscillator stops running.