Figure 1-5. pxi trigger bus connectivity diagram, System reference clock, System reference clock -10 – National Instruments NI PXIe-1075 User Manual

Page 17

Chapter 1

Getting Started

1-10

ni.com

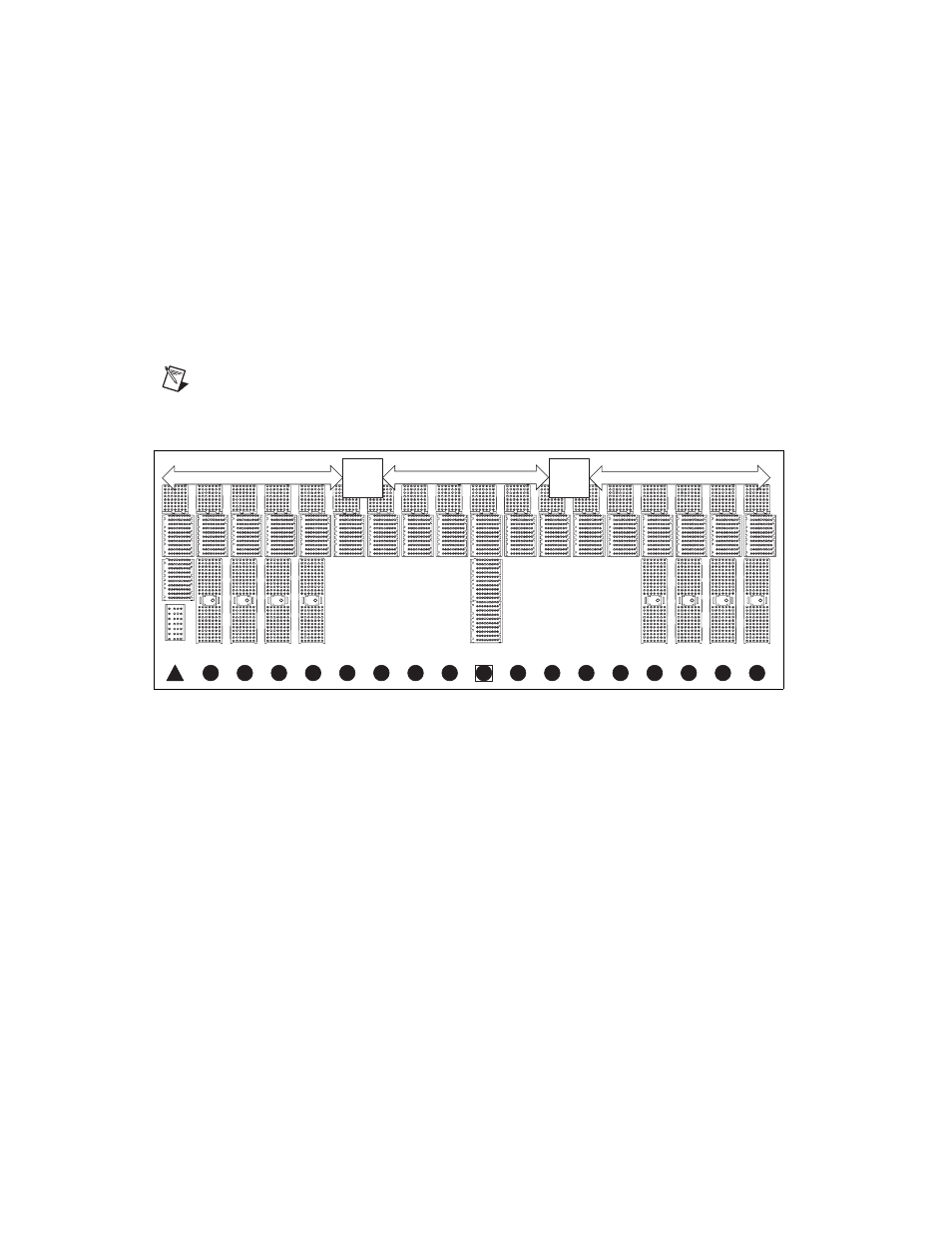

The PXI trigger lines from adjacent PXI trigger bus segments can be routed

in either direction across the PXI trigger bridges. Refer to Figure 1-5 for the

connectivity diagram. This allows you to send trigger signals to, and

receive trigger signals from, every slot in the chassis. Static trigger routing

(user-specified line and directional assignments) can be configured through

Measurement & Automation Explorer (MAX). Dynamic routing of triggers

(automatic line assignments) is supported through certain National

Instruments drivers like NI-DAQmx.

Note

Although any trigger line may be routed in either direction, it cannot be routed in

more than one direction at a time.

Figure 1-5. PXI Trigger Bus Connectivity Diagram

System Reference Clock

The PXIe-1075 chassis supplies PXI_CLK10, PXIe_CLK100 and

PXIe_SYNC100 to every peripheral slot with an independent driver for

each signal.

An independent buffer (having a source impedance matched to the

backplane and a skew of less than 1 ns between slots) drives PXI_CLK10

to each peripheral slot. You can use this common reference clock signal to

synchronize multiple modules in a measurement or control system.

PXI

Trigger

Bridge

PXI

Trigger

Bridge

PXI Trigger Bus Segment 2 (Slots 7-12)

PXI Trigger Bus Segment 1 (Slots 1-6)

PXI Trigger Bus Segment 3 (Slots 13-18)

0

H

H

H

H

H

H

H

H

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18