7 digital-in clock configuration, 8 thermal foldback control, Section 9.5.7 – NXP Semiconductors TFA9812 User Manual

Page 36: Section 9.5.8, In legacy control mode the def, Tfa9812, Nxp semiconductors

TFA9812_2

© NXP B.V. 2009. All rights reserved.

Preliminary data sheet

Rev. 02 — 22 January 2009

36 of 66

NXP Semiconductors

TFA9812

BTL stereo Class-D audio amplifier with I

2

S input

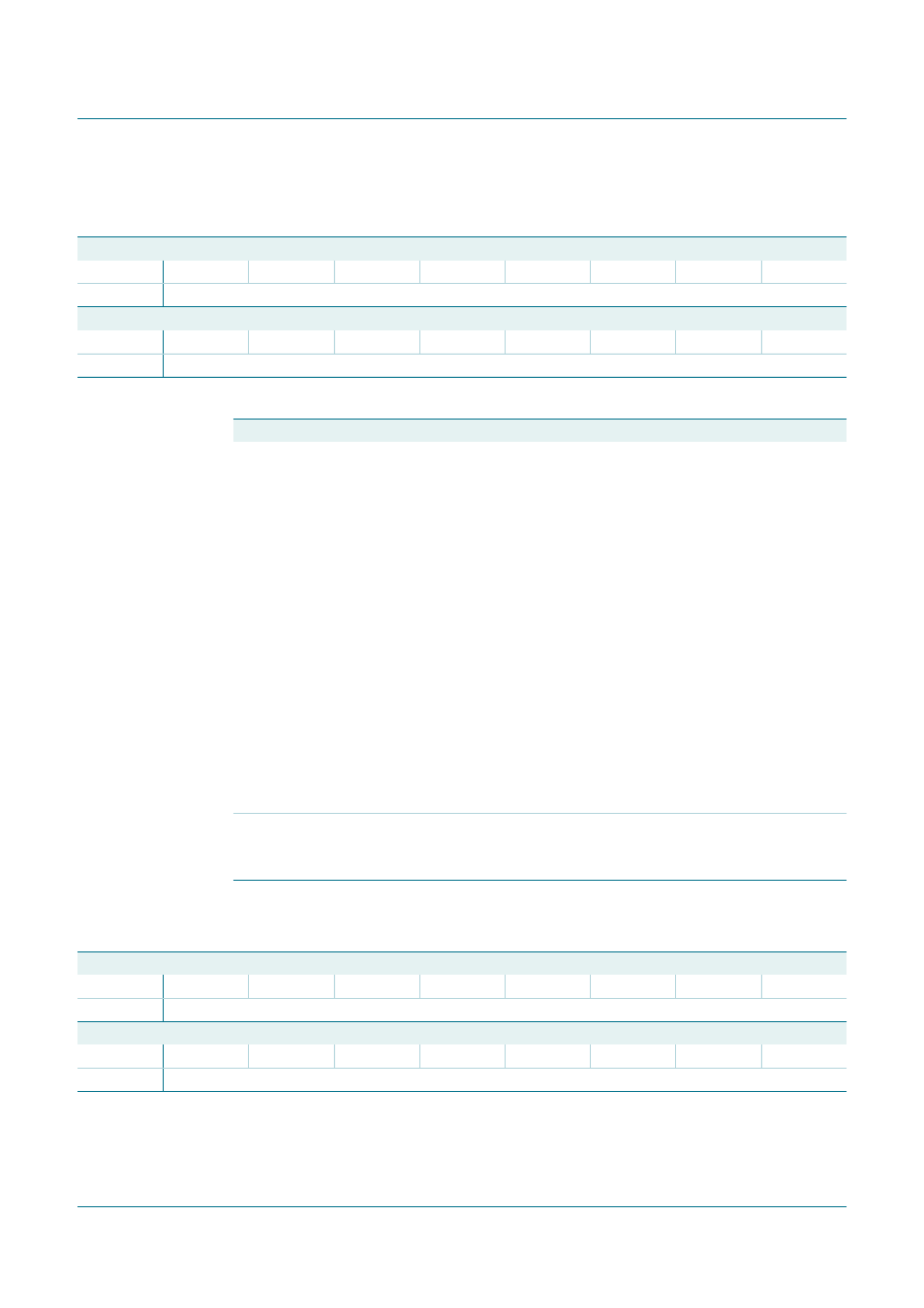

9.5.7 Digital-in clock configuration

9.5.8 Thermal foldback control

Table 43.

Register 2Dh: digital-in clock configuration

Bit

15

14

13

12

11

10

9

8

Symbol

RSD

RSD

RSD

RSD

RSD

RSD

RSD

RSD

Default

0

0

0

0

0

0

0

0

Bit

7

6

5

4

3

2

1

0

Symbol

RSD

RSD

RSD

FSUB3

FSUB2

FSUB1

FSUB0

DI_MS

Default

0

0

0

0

1

1

1

0

Table 44.

Bit description of register 2Dh:digital-in clock configuration

Bit

Symbol

Description

4 to 1

FSUB[3:0]

Sample frequency f

s

of digital-in signal:

0 = 8 kHz

1 = 11.025 kHz

2 = 12 kHz

3 = 16 kHz

4 = 22.05 kHz

5 = 24 kHz

6 = 32 kHz

7 = 44.1 kHz

8 = 48 kHz

9 = 64 kHz

10 = 88.2 kHz

11 = 96 kHz

12 = 128 kHz

13 = 176.4 kHz

14 = 192 kHz

15 = RSD

0

DI_MS

TFA9812 digital-in Master/Slave mode selection:

0 = Slave mode

1 = Master mode

Table 45.

Register 2Eh: thermal foldback control

Bit

15

14

13

12

11

10

9

8

Symbol

RSD

RSD

RSD

RSD

RSD

RSD

TP_THR9

TP_THR8

Default

0

0

0

0

0

0

0

0

Bit

7

6

5

4

3

2

1

0

Symbol

TP_THR7

TP_THR6

TP_THR5

TP_THR4

TP_THR3

TP_THR2

TP_THR1

TP_THR0

Default

0

0

0

0

0

0

0

0