6 pwm signal control, Section 9.5.6, The gain – NXP Semiconductors TFA9812 User Manual

Page 35: In legacy control mode tw, Table 40, Tfa9812, Nxp semiconductors

TFA9812_2

© NXP B.V. 2009. All rights reserved.

Preliminary data sheet

Rev. 02 — 22 January 2009

35 of 66

NXP Semiconductors

TFA9812

BTL stereo Class-D audio amplifier with I

2

S input

9.5.6 PWM signal control

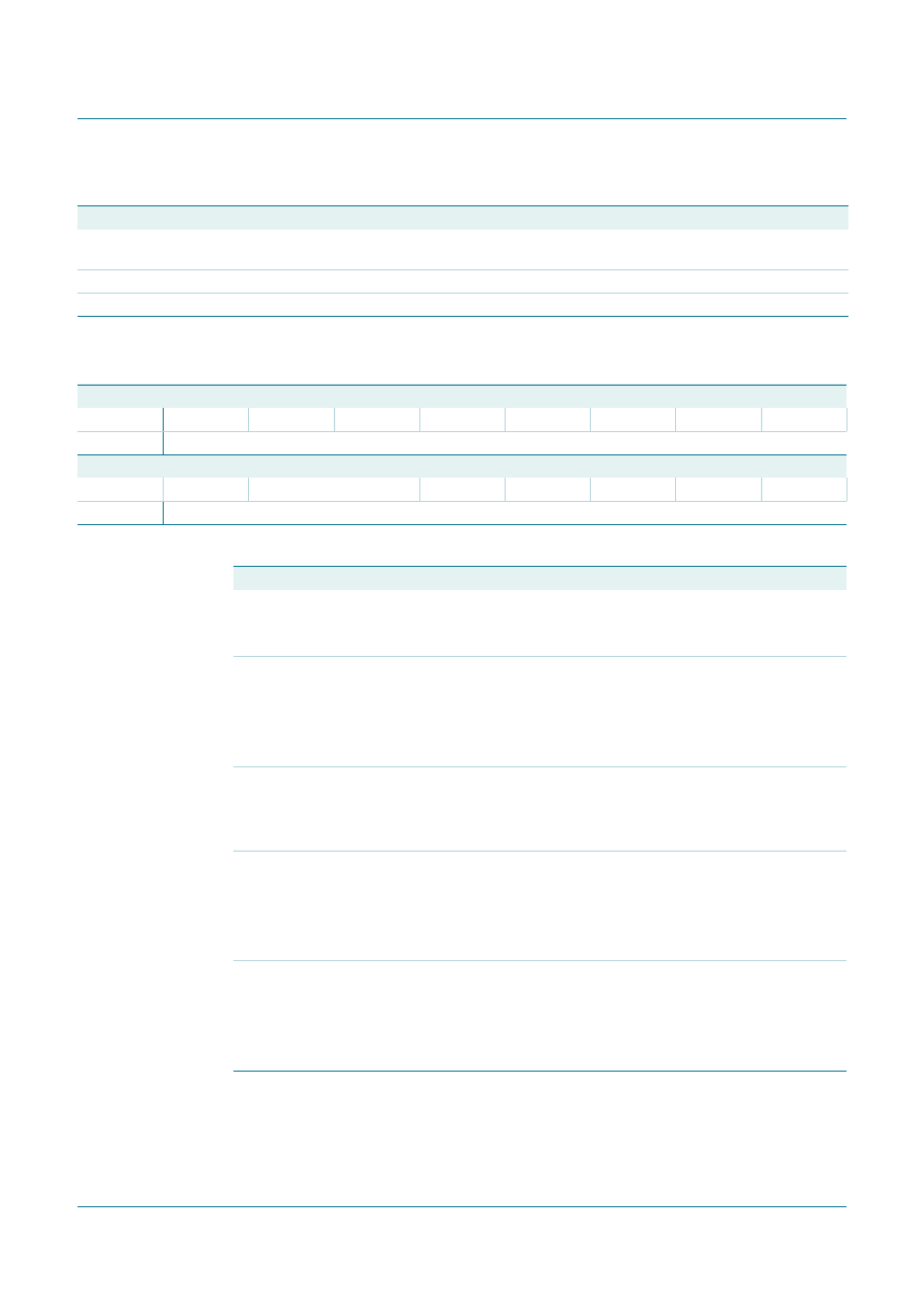

Table 40.

Default configuration equalizer for f

s

= 44.1 kHz

Band

A1/B1

A2/B2

A3/B3

A4/B4

A5/B5

C1/D1

C2/D2

C3/D3

C4/D4

C5/D5

Frequency

(Hz)

31

63

125

250

500

1000

2000

4000

8000

16000

Q-factor

1

1

1

1

1

1

1

1

1

1

Gain (dB)

0

0

0

0

0

0

0

0

0

0

Table 41.

Register 2Ch: PWM signal control

Bit

15

14

13

12

11

10

9

8

Symbol

RSD

RSD

RSD

RSD

RSD

RSD

RSD

RSD

Default

0

0

0

0

0

0

0

0

Bit

7

6

5

4

3

2

1

0

Symbol

RSD

PLIM1

PLIM0

PW_OFF

PW_SF1

PW_SF0

PW_CL1

PW_CL0

Default

0

0

0

0

0

1

0

1

Table 42.

Bit description address 2Ch

Bit

Symbol

Description

7

GAIN

+24 dB gain boost:

0 = Gain boost 0 dB

1 = Gain boost +24 dB

6 to 5

PLIM[1:0]

Output power limitation:

0 = Maximum power

1 = Maximum power

−

1.5 dB

2 = Maximum power

−

3.0 dB

3 = Maximum power

−

4.5 dB

4

PW_OFF

Hard mute control:

0 = No hard mute

1 = Hard mute enabled, implemented by PWM signal

with 50 % duty cycle

3 to 2

PW_SF[1:0]

PWM switching frequency:

0 = 350 kHz

1 = 400 kHz

2 = 700 kHz

3 = 750 kHz

1 to 0

PW_CL[1:0]

PWM clip level:

0 = < 0.5 % THD

1 = 10 % THD

2 = 20 % THD

3 = 30 % THD