Figure 9, Tfa9812, Nxp semiconductors – NXP Semiconductors TFA9812 User Manual

Page 34

TFA9812_2

© NXP B.V. 2009. All rights reserved.

Preliminary data sheet

Rev. 02 — 22 January 2009

34 of 66

NXP Semiconductors

TFA9812

BTL stereo Class-D audio amplifier with I

2

S input

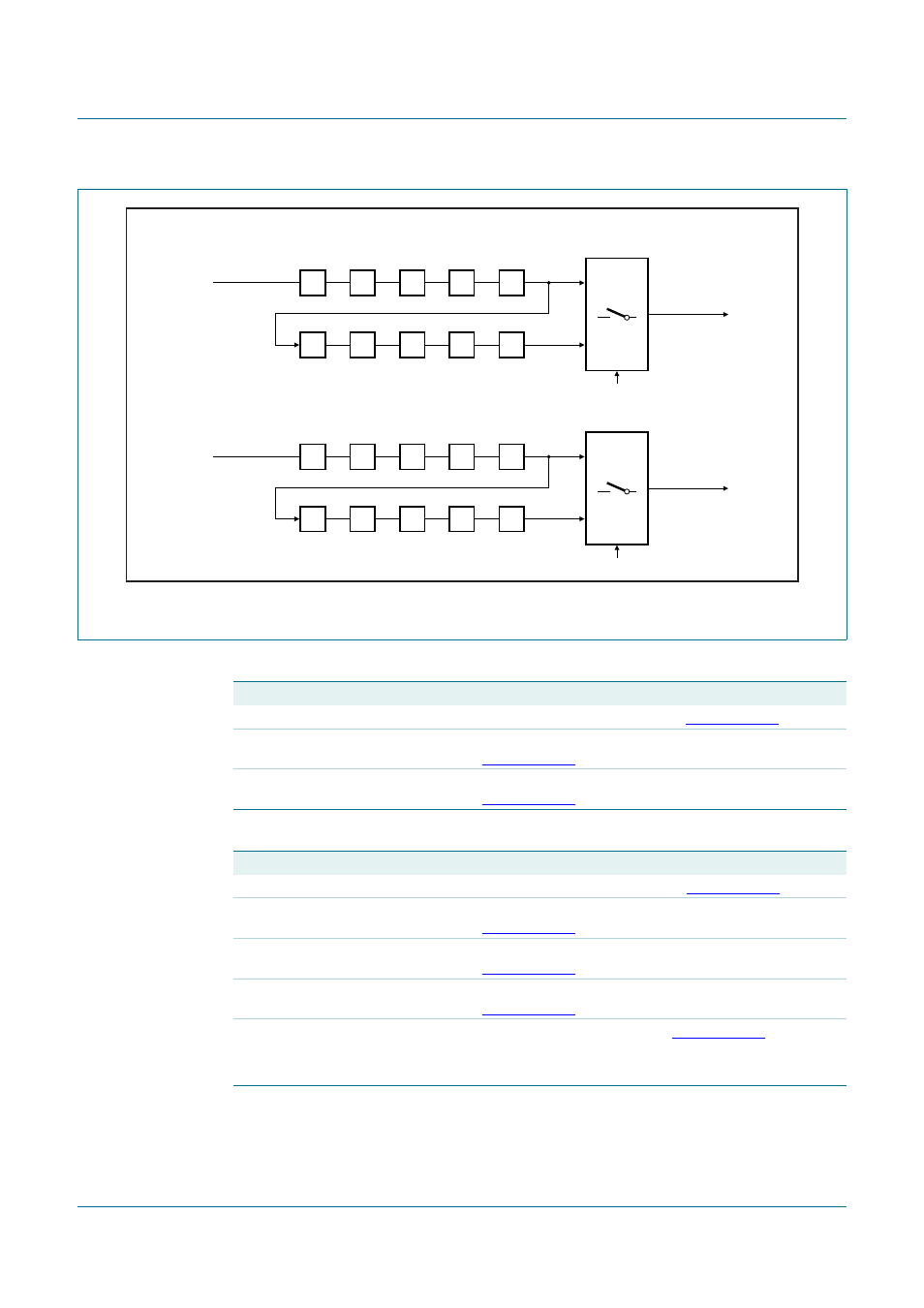

Fig 9.

Equalizer configuration and register location mapping

Left in

Left out

2

×

5 or 2

×

10

Right in

Right out

2

×

5 or 2

×

10

A1

C1

B1

D1

D2

D3

D4

D5

B2

B3

B4

B5

C2

C3

C4

C5

A2

A3

A4

A5

010aaa404

Table 38.

Bit description of registers xxh = 04, 06...2A

Bit

Symbol

Description

15

Eyy_t

1

The filter configuration bit t

1,

see

14 to 4

Eyy_k1

m

[10:0]

The 11 mantissa bits of the filter parameter k

1,

see

3 to 0

Eyy_k1

e

[3:0]

The four exponent bits of the filter parameter k

1

, see

Table 39.

Bit description of registers xxh = 05, 07...2B

Bit

Symbol

Description

15

Eyy_t

2

The filter configuration bit t

2

, see

.

14 to 11

Eyy_k

2m

[3:0]

The four mantissa bits of the filter parameter k

2

, see

10 to 8

Eyy_k

2e

[2:0]

The three exponent bits of the filter parameter k

2

, see

7 to 1

Eyy_k

0

[6:0]

The seven bits of the filter gain parameter k

0

, see

0

Eyy_s

The filter scale-factor bits, see

:

0 = No scaling applied

1 =

−

6 dB amplification enabled