Appendix d – cpld pinout, Cpld pinout – Pico Communications E-14 User Manual

Page 30

E‐14 Hardware Reference Manual

www.picocomputing.com

Pico Computing, Inc.

30

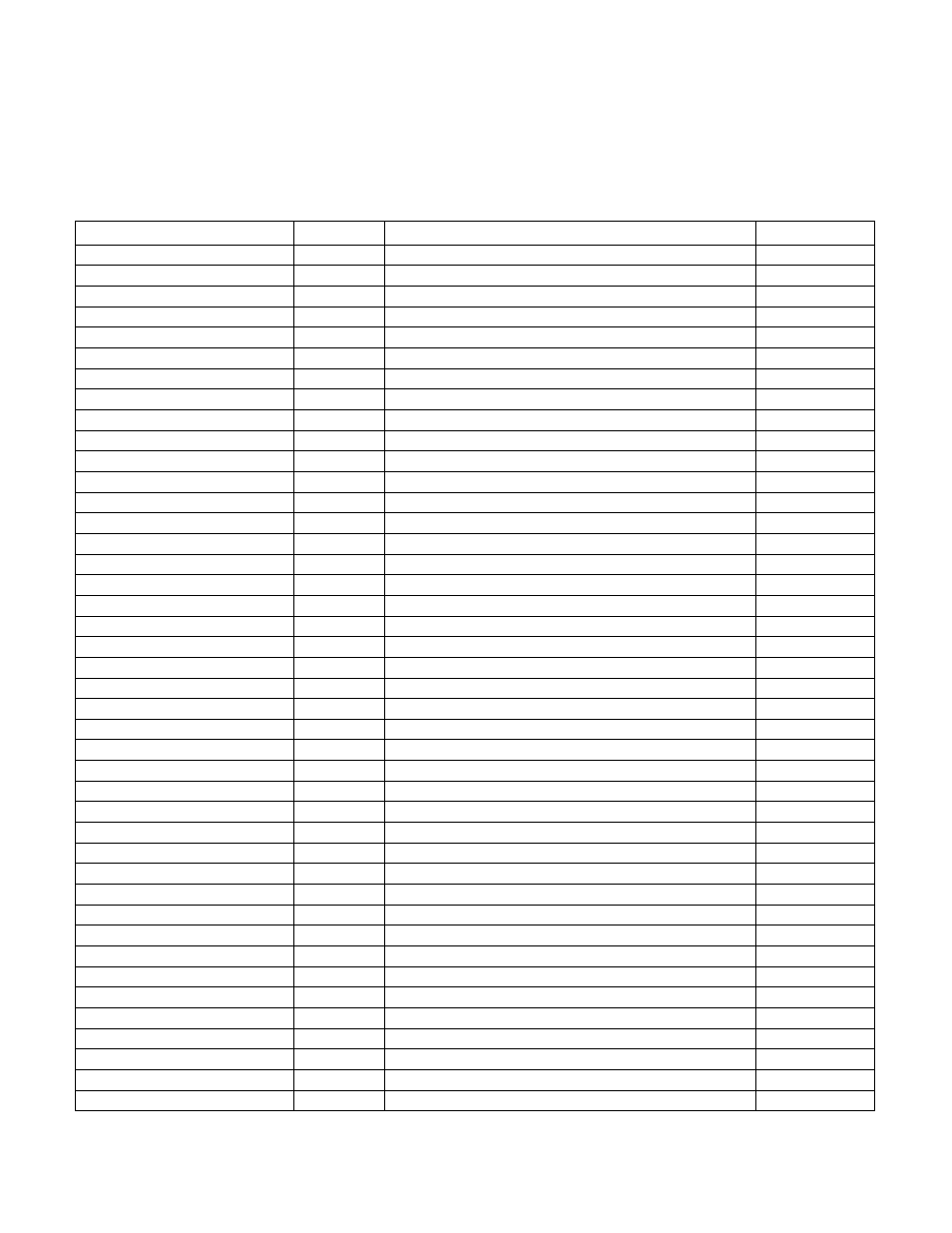

Appendix D – CPLD Pinout

CPLD Pinout

Net

Pin

Description

Direction

50MHZ_CLOCK

K2

50 MHz Clock In +/‐ 50 ppm

I

CPLD_TDI

J10

CPLD JTAG TDI

O

ETHER_TDI

A6

Ethernet JTAG TDI

O

F\L\A\S\H\_\B\Y\T\E\

K7

8/16 Bit Mode Select

O

F\L\A\S\H\_\O\E\

A8

Output Enable

O

F\L\A\S\H\_\R\E\S\E\T\

A2

Flash Reset

O

F\L\A\S\H\_\W\E\

A3

Flash Write Enable

O

F\L\A\S\H\_\W\P\

A4

Flash Write Protect

O

F\L\A\S\H\_C\E\

A9

Flash Chip Enable

O

F\P\G\A\_\P\R\O\G\

A5

FPGA Asynchronous Reset

O

FLASH_A0

K8

Address 1 [8 Bit Mode]

O

FLASH_A1

K1

Address 2

I/O

FLASH_A2

H1

Address 3

I/O

FLASH_A3

F1

Address 4

I/O

FLASH_A4

K4

Address 5

I/O

FLASH_A5

C3

Address 6

I/O

FLASH_A6

G3

Address 7

I/O

FLASH_A7

H3

Address 8

I/O

FLASH_A8

A7

Address 9

I/O

FLASH_A9

J1

Address 10

I/O

FLASH_A10

H10

Address 11

I/O

FLASH_A11

G1

Address 12

I/O

FLASH_A12

D1

Address 13

I/O

FLASH_A13

C1

Address 14

I/O

FLASH_A14

K5

Address 15

I/O

FLASH_A15

E1

Address 16

I/O

FLASH_A16

A1

Address 17

I/O

FLASH_A17

B1

Address 18

I/O

FLASH_A18

A10

Address 19

I/O

FLASH_A19

E3

Address 20

I/O

FLASH_A20

F3

Address 21

I/O

FLASH_A21

C5

Address 22

I/O

FLASH_A22

B10

Address 23

I/O

FLASH_A23

C4

Address 24

I/O

FLASH_A24

D8

Address 25

I/O

FLASH_A25

C8

Address 26

I/O

FLASH_D15

G10

Address 0*

I/O

FPGA_CCLK

F10

FPGA Configuration Clock

O

FPGA_DONE

D10

FPGA Done Programming

I

FPGA_INIT

E10

FPGA Ready to Program

I/O

LOAD

K6

Load Image Request

I

PEEKABOO

H5

Output Last Address Before Done Request

I