Pico Communications E-14 User Manual

Page 28

E‐14 Hardware Reference Manual

www.picocomputing.com

Pico Computing, Inc.

28

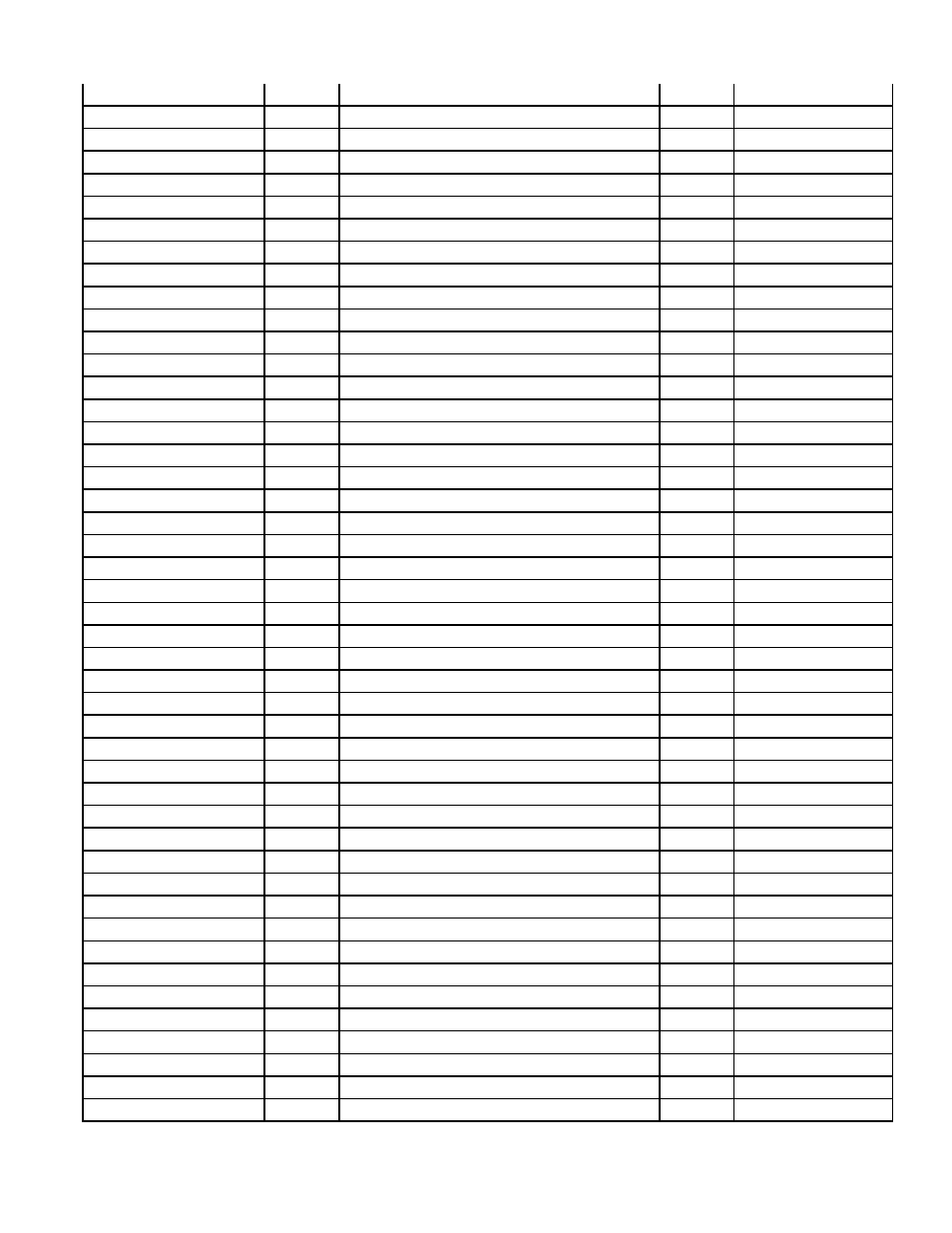

RAM_A7

E22

Address 7

O

SSTL18_II_DCI

RAM_A8

D24

Address 8

O

SSTL18_II_DCI

RAM_A9

F20

Address 9

O

SSTL18_II_DCI

RAM_A10

F23

Address 10

O

SSTL18_II_DCI

RAM_A11

A14

Address 11

O

SSTL18_II_DCI

RAM_A12

D23

Address 12 [MSB]

O

SSTL18_II_DCI

RAM_BA0

E23

Bank Address 0

O

SSTL18_II_DCI

RAM_BA1

K18

Bank Address 1

O

SSTL18_II_DCI

RAM_CLK

C14

Clock

O

SSTL18_II_DCI

RAM_CLK

F15

Clock Feedback

I

SSTL18_II_DCI

RAM_CLKE0

A15

Clock Enable 0[Power Save Mode]

O

SSTL18_II_DCI

RAM_CLKE1

G22

Clock Enable 1[Power Save Mode]

O

SSTL18_II_DCI

RAM_D0

C19

Data 0 (LSB)

I/O

SSTL18_II_DCI

RAM_D1

F18

Data 1

I/O

SSTL18_II_DCI

RAM_D2

G20

Data 2

I/O

SSTL18_II_DCI

RAM_D3

D19

Data 3

I/O

SSTL18_II_DCI

RAM_D4

C21

Data 4

I/O

SSTL18_II_DCI

RAM_D5

E20

Data 5

I/O

SSTL18_II_DCI

RAM_D6

F17

Data 6

I/O

SSTL18_II_DCI

RAM_D7

B17

Data 7

I/O

SSTL18_II_DCI

RAM_D8

D15

Data 8

I/O

SSTL18_II_DCI

RAM_D9

D14

Data 9

I/O

SSTL18_II_DCI

RAM_D10

C16

Data 10

I/O

SSTL18_II_DCI

RAM_D11

A17

Data 11

I/O

SSTL18_II_DCI

RAM_D12

G17

Data 12

I/O

SSTL18_II_DCI

RAM_D13

B16

Data 13

I/O

SSTL18_II_DCI

RAM_D14

C12

Data 14

I/O

SSTL18_II_DCI

RAM_D15

B12

Data 15

I/O

SSTL18_II_DCI

RAM_D16

H19

Data 16

I/O

SSTL18_II_DCI

RAM_D17

H22

Data 17

I/O

SSTL18_II_DCI

RAM_D18

G24

Data 18

I/O

SSTL18_II_DCI

RAM_D19

H24

Data 19

I/O

SSTL18_II_DCI

RAM_D20

J21

Data 20

I/O

SSTL18_II_DCI

RAM_D21

G19

Data 21

I/O

SSTL18_II_DCI

RAM_D22

K20

Data 22

I/O

SSTL18_II_DCI

RAM_D23

K23

Data 23

I/O

SSTL18_II_DCI

RAM_D24

M22

Data 24

I/O

SSTL18_II_DCI

RAM_D25

M24

Data 25

I/O

SSTL18_II_DCI

RAM_D26

K21

Data 26

I/O

SSTL18_II_DCI

RAM_D27

L24

Data 27

I/O

SSTL18_II_DCI

RAM_D28

N22

Data 28

I/O

SSTL18_II_DCI

RAM_D29

L19

Data 29

I/O

SSTL18_II_DCI

RAM_D30

N24

Data 30

I/O

SSTL18_II_DCI

RAM_D31

J23

Data 31

I/O

SSTL18_II_DCI

RAM_DM0‐7

E17

Data Mask [0‐7]

O

SSTL18_II_DCI

RAM_DM8‐15

C13

Data Mask [8‐15]

O

SSTL18_II_DCI