Appendix c – fpga pinout, Fpga pinout – Pico Communications E-14 User Manual

Page 23

E‐14 Hardware Reference Manual

www.picocomputing.com

Pico Computing, Inc.

23

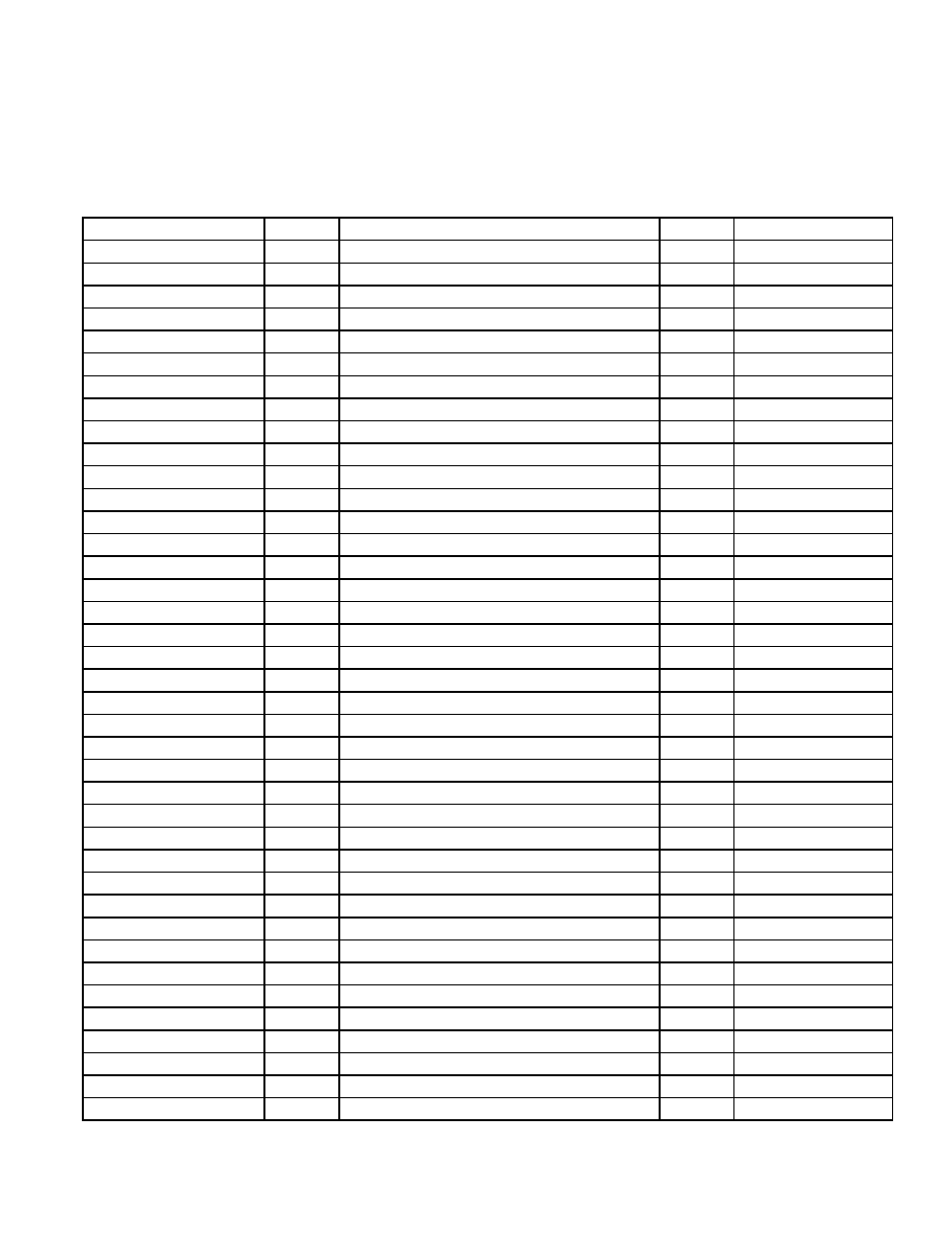

Appendix C – FPGA Pinout

FPGA Pinout

50MHZ_CLOCK

AA14

50 MHz Clock In +/‐ 50 ppm

I

LV_TTL 3.3V

50MHZ_CLOCK

AB12

50 MHz Clock In +/‐ 50 ppm

I

LV_TTL 3.3V

50MHZ_CLOCK

AB14

50 MHz Clock In +/‐ 50 ppm

I

LV_TTL 3.3V

50MHZ_CLOCK

AC13

50 MHz Clock In +/‐ 50 ppm

I

LV_TTL 3.3V

50MHZ_CLOCK

AD15

50 MHz Clock In +/‐ 50 ppm

I

LV_TTL 3.3V

50MHZ_CLOCK

AE13

50 MHz Clock In +/‐ 50 ppm

I

LV_TTL 3.3V

ADC_AMP_PWUP

AD14

A/D Amplifier Power Up

O

LV_TTL 3.3V

ADC_CLK

V23

Clock

O

LV_CMOS 2.5V

ADC_D0

W23

Data 0 [LSB]

I

LV_CMOS 2.5V

ADC_D1

T24

Data 1

I

LV_CMOS 2.5V

ADC_D2

V21

Data 2

I

LV_CMOS 2.5V

ADC_D3

W18

Data 3

I

LV_CMOS 2.5V

ADC_D4

Y22

Data 4

I

LV_CMOS 2.5V

ADC_D5

W20

Data 5

I

LV_CMOS 2.5V

ADC_D6

AB21

Data 6

I

LV_CMOS 2.5V

ADC_D7

Y18

Data 7

I

LV_CMOS 2.5V

ADC_D8

AB20

Data 8

I

LV_CMOS 2.5V

ADC_D9

AC21

Data 9

I

LV_CMOS 2.5V

ADC_D10

T20

Data 10

I

LV_CMOS 2.5V

ADC_D11

R20

Data 11

I

LV_CMOS 2.5V

ADC_D12

R21

Data 12

I

LV_CMOS 2.5V

ADC_D13

V18

Data 13 [MSB]

I

LV_CMOS 2.5V

ADC_MODE

T17

Data Format Select

O

LV_CMOS 2.5V

ADC_OTR

T18

Out‐of‐Range Indicator

O

LV_CMOS 2.5V

ADC_PDWN

V22

Power Down A/D Controller

O

LV_CMOS 2.5V

CB_CAD0

K3

CardBus Data/Address 0

I/O

LV_TTL 3.3V

CB_CAD1

F3

CardBus Data/Address 1

I/O

LV_TTL 3.3V

CB_CAD2

D3

CardBus Data/Address 2

I/O

LV_TTL 3.3V

CB_CAD3

C3

CardBus Data/Address 3

I/O

LV_TTL 3.3V

CB_CAD4

M6

CardBus Data/Address 4

I/O

LV_TTL 3.3V

CB_CAD5

L7

CardBus Data/Address 5

I/O

LV_TTL 3.3V

CB_CAD6

K7

CardBus Data/Address 6

I/O

LV_TTL 3.3V

CB_CAD7

J4

CardBus Data/Address 7

I/O

LV_TTL 3.3V

CB_CAD8

G5

CardBus Data/Address 8

I/O

LV_TTL 3.3V

CB_CAD9

G9

CardBus Data/Address 9

I/O

LV_TTL 3.3V

CB_CAD10

F7

CardBus Data/Address 10

I/O

LV_TTL 3.3V

CB_CAD11

F8

CardBus Data/Address 11

I/O

LV_TTL 3.3V

CB_CAD12

D4

CardBus Data/Address 12

I/O

LV_TTL 3.3V

CB_CAD13

C4

CardBus Data/Address 13

I/O

LV_TTL 3.3V

CB_CAD14

D5

CardBus Data/Address 14

I/O

LV_TTL 3.3V