Watchdog timer – Philips P89LPC903 User Manual

Page 86

Philips Semiconductors

User’s Manual - Preliminary -

P89LPC901/902/903

WATCHDOG TIMER

2003 Dec 8

86

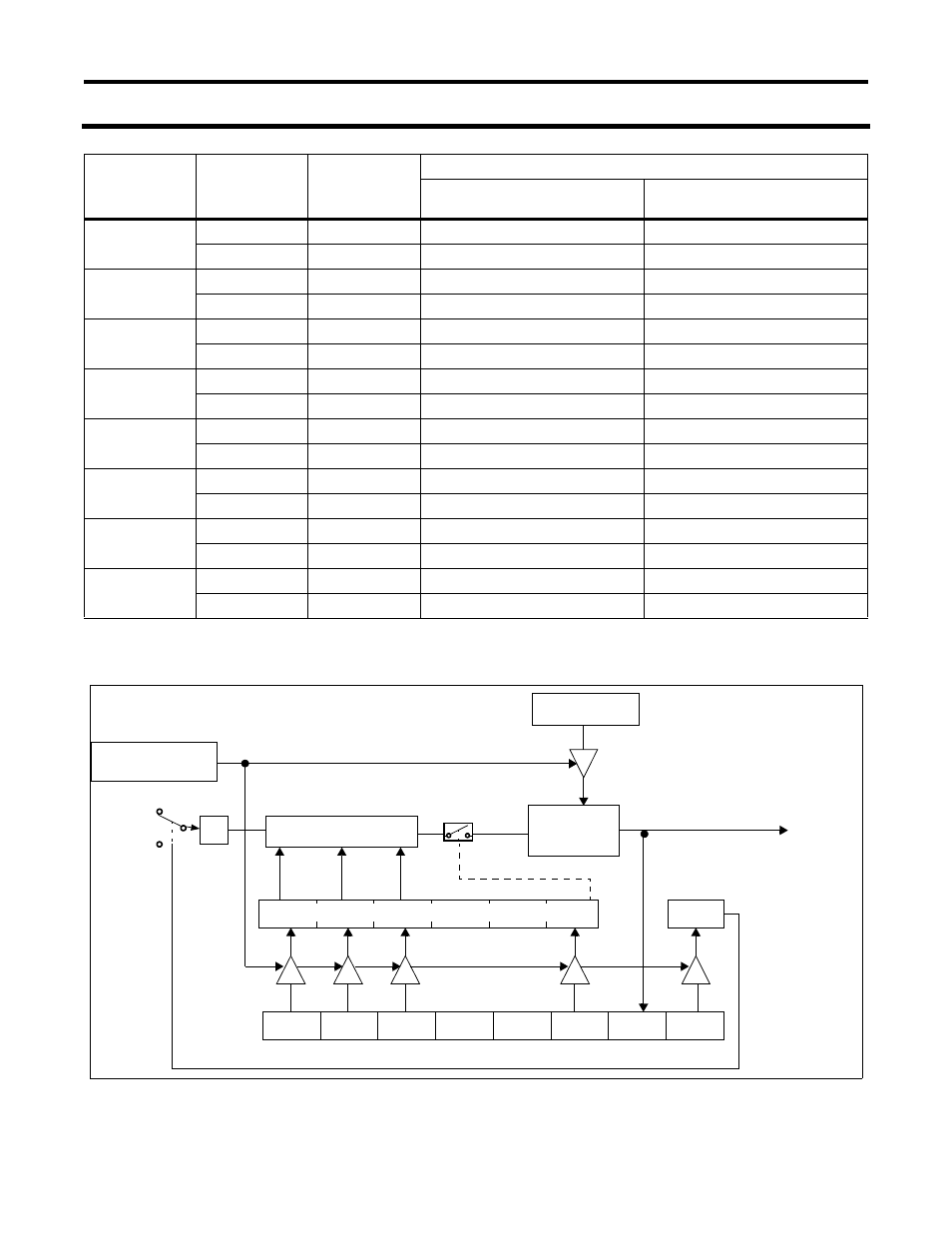

Table 12-2: P89LPC901/902/903 Watchdog Timeout Values

Figure 12-3: Watchdog Timer in Watchdog Mode (WDTE = 1)

PRE2-PRE0

WDL in decimal)

Timeout Period

(in watchdog clock

cycles)

Watchdog Clock Source

400KHz Watchdog Oscillator Clock

(Nominal)

12MHz CCLK (6MHz CCLK/2

Watchdog Clock)

000

0

33

82.5µs

5.50µs

255

8,193

20.5ms

1.37ms

001

0

65

162.5µs

10.8µs

255

16,385

41.0ms

2.73ms

010

0

129

322.5µs

21.5µs

255

32,769

81.9ms

5.46ms

011

0

257

642.5µs

42.8µs

255

65,537

163.8ms

10.9ms

100

0

513

.1.28ms

85.5µs

255

131,073

327.7ms

21.8ms

101

0

1,025

2.56ms

170.8µs

255

262,145

655.4ms

43.7ms

110

0

2,049

5.12ms

341.5µs

255

524,289

1.31s

87.4ms

111

0

4097

10.2ms

682.8µs

255

1,048,577

2.62s

174.8ms

8-Bit Down

Counter

MOV WFEED1, #0A5H

MOV WFEED2, #05AH

WDL (C1H)

PRE2

PRE1

PRE0

WDRUN

WDTOF

WDCLK

SHADOW

REGISTER FOR

WDCON

WDCON(A7H)

PRESCALER

RESET

control register

Watchdog reset can also be caused

by an invalid feed sequence, or by

writing to WDCON not immediately

followed by a feed sequence

Watchdog

Oscillator

PCLK

ч32