Clocks, Watchdog oscillator option – Philips P89LPC903 User Manual

Page 29

Philips Semiconductors

User’s Manual - Preliminary -

P89LPC901/902/903

CLOCKS

2003 Dec 8

29

If CCLK is 8MHz or slower, the CLKLP SFR bit (AUXR1.7) can be set to ’1’ to reduce power consumption. On reset, CLKLP is

’0’ allowing highest performance access. This bit can then be set in software if CCLK is running at 8MHz or slower.

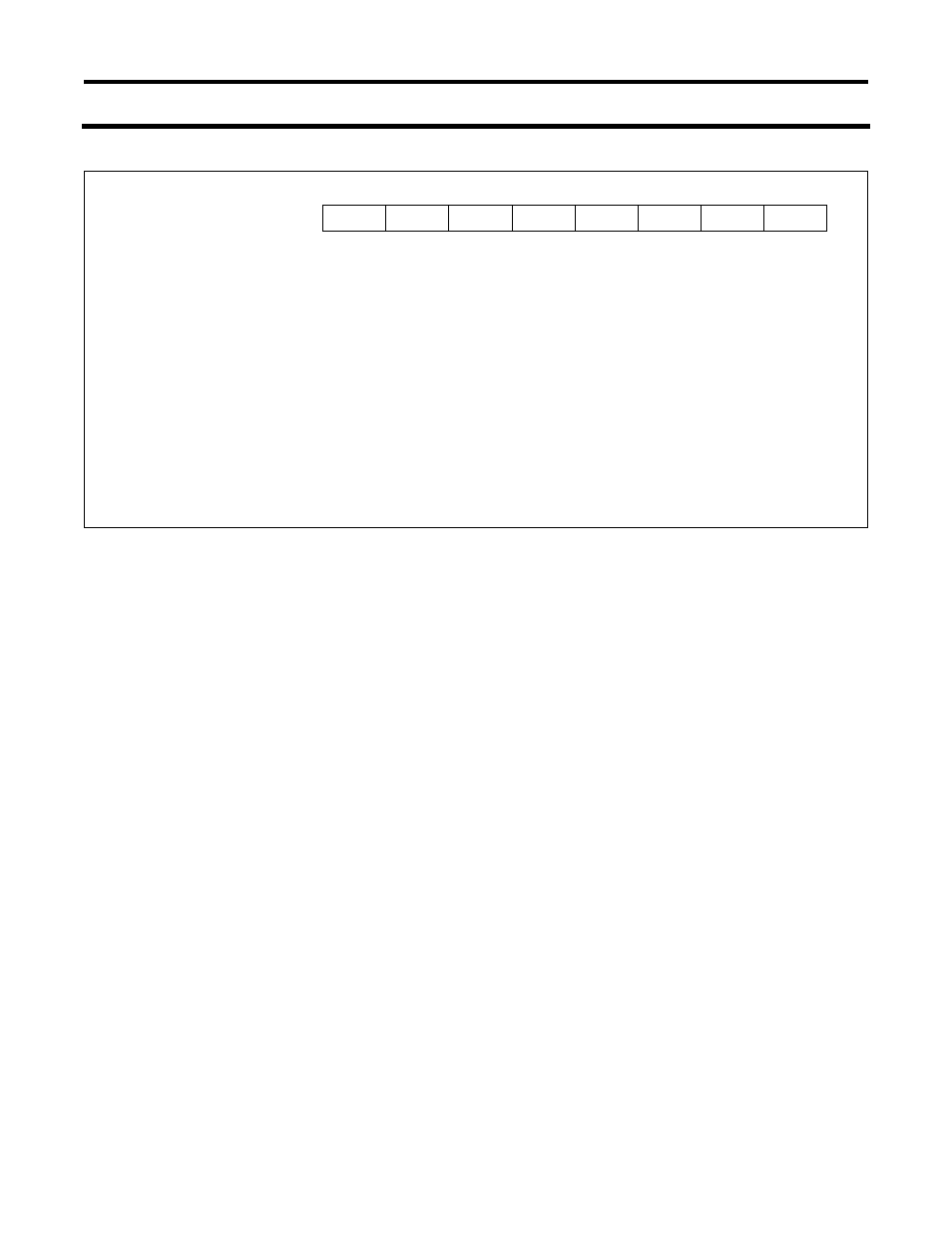

Figure 2-2: On-Chip RC Oscillator TRIM Register

Watchdog Oscillator Option

The watchdog has a separate oscillator which has a nominal frequency of 400KHz. This oscillator can be used to save power

when a high clock frequency is not needed.

External Clock Input Option - P89LPC901

In this configuration, the processor clock is derived from an external source driving the XTAL1 / P3.1 pin. The rate may be from

0 Hz up to 12 MHz. The XTAL2 / P3.0 pin may be used as a standard port pin or a clock output.

TRIM

Address: 96h

Not bit addressable

Reset Source(s): Power-up only

Reset Value: On power-up reset, ENCLK = 0, and TRIM.5-0 are loaded with the factory programmed value.

BIT

SYMBOL

FUNCTION

TRIM.7

-

Reserved.

TRIM.6

ENCLK

When ENCLK =1, CCLK/ 2 is output on the XTAL2 pin (P3.0) provided that the crystal

oscillator is not being used. When ENCLK=0, no clock output is enabled.(P89LPC901).

TRIM.5-0

Trim value.

Note: on reset, the TRIM SFR is initialized with a factory preprogrammed value. When setting or clearing either the ENCLK

or RCCLK bits, the user should retain the contents of bits 5:0 of the TRIM register. This can be done by reading the contents

of the TRIM register (into the ACC for example), modifying bits 6 or 7, and writing this result back into the TRIM register.

Alternatively, the "ANL direct" or "ORL direct" instructions can be used to clear or set bit 6 or 7of the TRIM register.

7

6

5

4

3

2

1

0

-

ENCLK

TRIM.5

TRIM.4

TRIM.3

TRIM.2

TRIM.1

TRIM.0