Si5351a/b/c – Silicon Laboratories SI5351A/B/C User Manual

Page 59

Si5351A/B/C

Preliminary Rev. 0.95

59

Reset value = 0000 0000

Reset value = 0000 0000

Reset value = 0000 0000

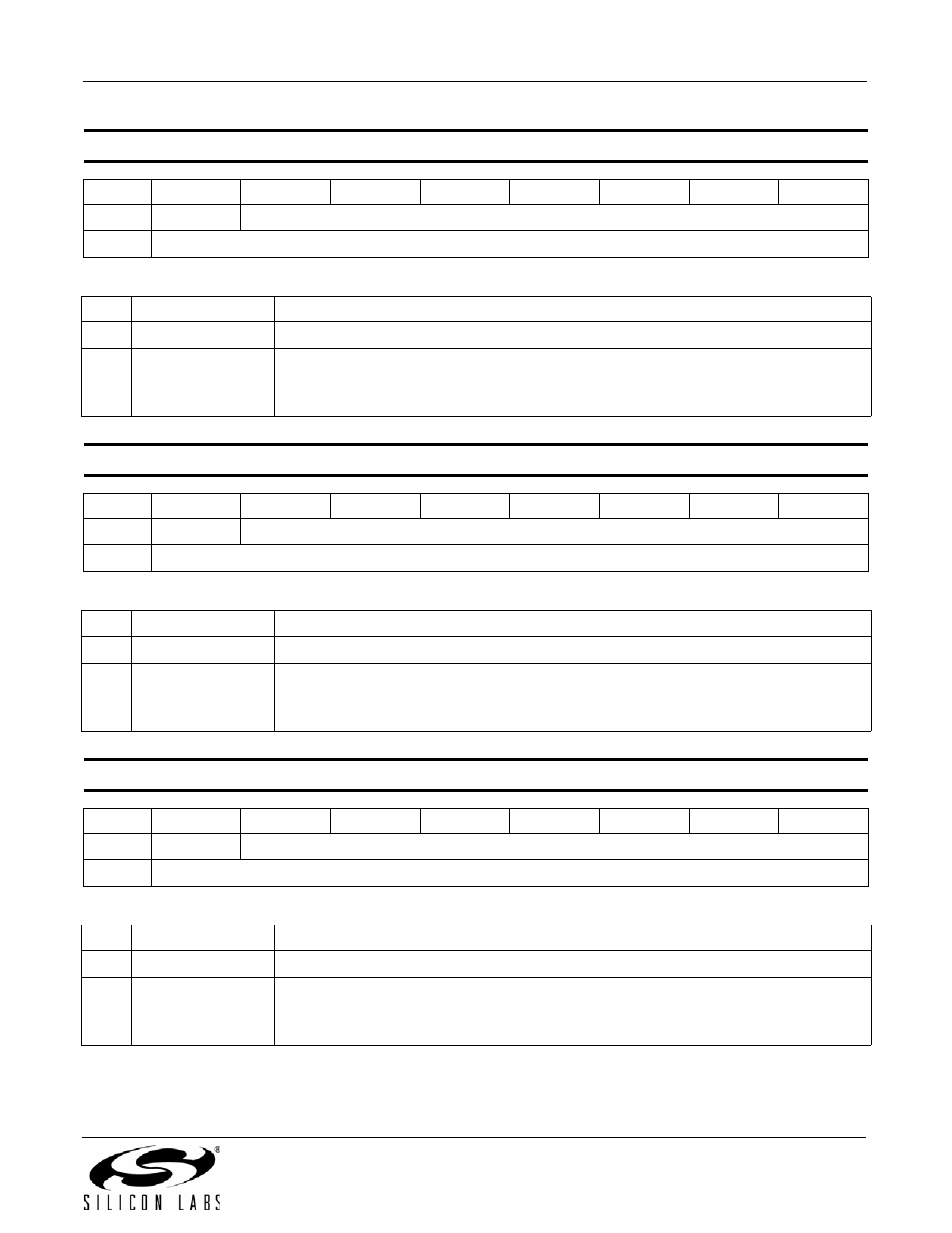

Register 165. CLK0 Initial Phase Offset

Bit

D7

D6

D5

D4

D3

D2

D1

D0

Name

CLK0_PHOFF[6:0]

Type

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Bit

Name

Function

7

Reserved

Only write 0 to this bit.

6:0

CLK0_PHOFF[6:0] Clock 0 Initial Phase Offset.

CLK0_PHOFF[6:0] is an unsigned integer with one LSB equivalent to a time delay of

Tvco/4, where Tvco is the period of the VCO/PLL associated with this output.

Register 166. CLK1 Initial Phase Offset

Bit

D7

D6

D5

D4

D3

D2

D1

D0

Name

CLK1_PHOFF[6:0]

Type

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Bit

Name

Function

7

Reserved

Only write 0 to this bit.

6:0

CLK1_PHOFF[6:0] Clock 1 Initial Phase Offset.

CLK1_PHOFF[6:0] is an unsigned integer with one LSB equivalent to a time delay of

Tvco/4, where Tvco is the period of the VCO/PLL associated with this output.

Register 167. CLK2 Initial Phase Offset

Bit

D7

D6

D5

D4

D3

D2

D1

D0

Name

CLK2_PHOFF[6:0]

Type

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Bit

Name

Function

7

Reserved

Only write 0 to this bit.

6:0

CLK2_PHOFF[6:0] Clock 2 Initial Phase Offset.

CLK2_PHOFF[6:0] is an unsigned integer with one LSB equivalent to a time delay of

Tvco/4, where Tvco is the period of the VCO/PLL associated with this output.