Register map summary, Own in section 7, Si5351a/b/c – Silicon Laboratories SI5351A/B/C User Manual

Page 23

Si5351A/B/C

Preliminary Rev. 0.95

23

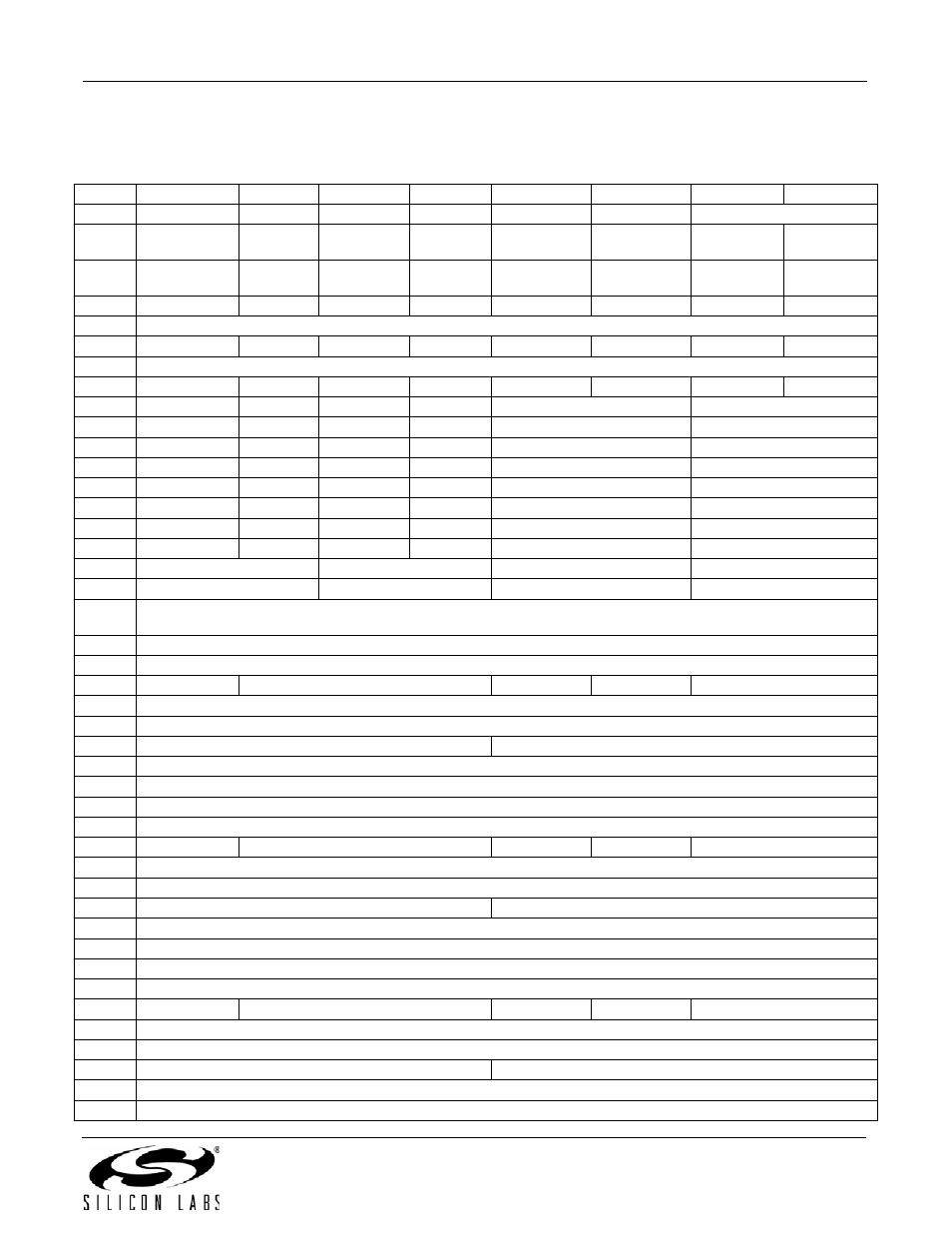

7. Register Map Summary

The following is a summary of the register map used to read status, control, and configure the Si5351.

Register

7

6

5

4

3

2

1

0

0

SYS_INIT

LOL_B

LOL_A

LOS

REVID[1:0]

1

SYSCAL_

STKY

LOS_B_

STKY

LOL_A_

STKY

LOS_

STKY

2

SYSCAL_

MASK

LOS_B_

MASK

LOL_A _

MASK

LOS_

MASK

3

CLK7_EN

CLK6_EN

CLK5_EN

CLK4_EN

CLK3_EN

CLK2_EN

CLK1_EN

CLK0_EN

4–8

Reserved

9

OEB_CLK7

OEB_CLK6

OEB_CLK5

OEB_CLK4

OEB_CLK3

OEB_CLK2

OEB_CLK1

OEB_CLK0

10–14

Reserved

15

0

0

0

0

PLLB_SRC

PLLA_SRC

0

0

16

CLK0_PDN

MS0_INT

MS0_SRC

CLK0_INV

CLK0_SRC[1:0]

CLK0_IDRV[1:0]

17

CLK1_PDN

MS1_INT

MS1_SRC

CLK1_INV

CLK1_SRC[1:0]

CLK1_IDRV[1:0]

18

CLK2_PDN

MS2_INT

MS2_SRC

CLK2_INV

CLK2_SRC[1:0]

CLK2_IDRV[1:0]

19

CLK3_PDN

MS3_INT

MS3_SRC

CLK3_INV

CLK3_SRC[1:0]

CLK3_IDRV[1:0]

20

CLK4_PDN

MS4_INT

MS4_SRC

CLK4_INV

CLK4_SRC[1:0]

CLK4_IDRV[1:0]

21

CLK5_PDN

MS5_INT

MS5_SRC

CLK5_INV

CLK5_SRC[1:0]

CLK5_IDRV[1:0]

22

CLK6_PDN

FBA_INT

MS6_SRC

CLK6_INV

CLK6_SRC[1:0]

CLK6_IDRV[1:0]

23

CLK7_PDN

FBB_INT

MS6_SRC

CLK7_INV

CLK7_SRC[1:0]

CLK7_IDRV[1:0]

24

CLK3_DIS_STATE

CLK2_DIS_STATE

CLK1_DIS_STATE

CLK0_DIS_STATE

25

CLK7_DIS_STATE

CLK6_DIS_STATE

CLK5_DIS_STATE

CLK4_DIS_STATE

26–41

PLL, MultiSynth, and output clock delay offset Configuration Registers.

Use ClockBuilder Desktop Software to Determine These Register Values.

42

MS0_P3[15:8]

43

MS0_P3[7:0]

44

R0_DIV[2:0]

MS0_P1[17:16]

45

MS0_P1[15:8]

46

MS0_P1[7:0]

47

MS0_P3[19:16]

MS0_P2[19:16]

48

MS0_P2[15:8]

49

MS0_P2[7:0]

50

MS1_P3[15:8]

51

MS1_P3[7:0]

52

R1_DIV[2:0]

MS1_P1[17:16]

53

MS1_P1[15:8]

54

MS1_P1[7:0]

55

MS1_P3[19:16]

MS1_P2[19:16]

56

MS1_P2[15:8]

57

MS1_P2[7:0]

58

MS2_P3[15:8]

59

MS2_P3[7:0]

60

R2_DIV[2:0]

MS2_P1[17:16]

61

MS2_P1[15:8]

62

MS2_P1[7:0]

63

MS2_P3[19:16]

MS2_P2[19:16]

64

MS2_P2[15:8]

65

MS2_P2[7:0]