S i 5 3 5 1 a / b / c – Silicon Laboratories SI5351A/B/C User Manual

Page 36

S i 5 3 5 1 A / B / C

36

Preliminary Rev. 0.95

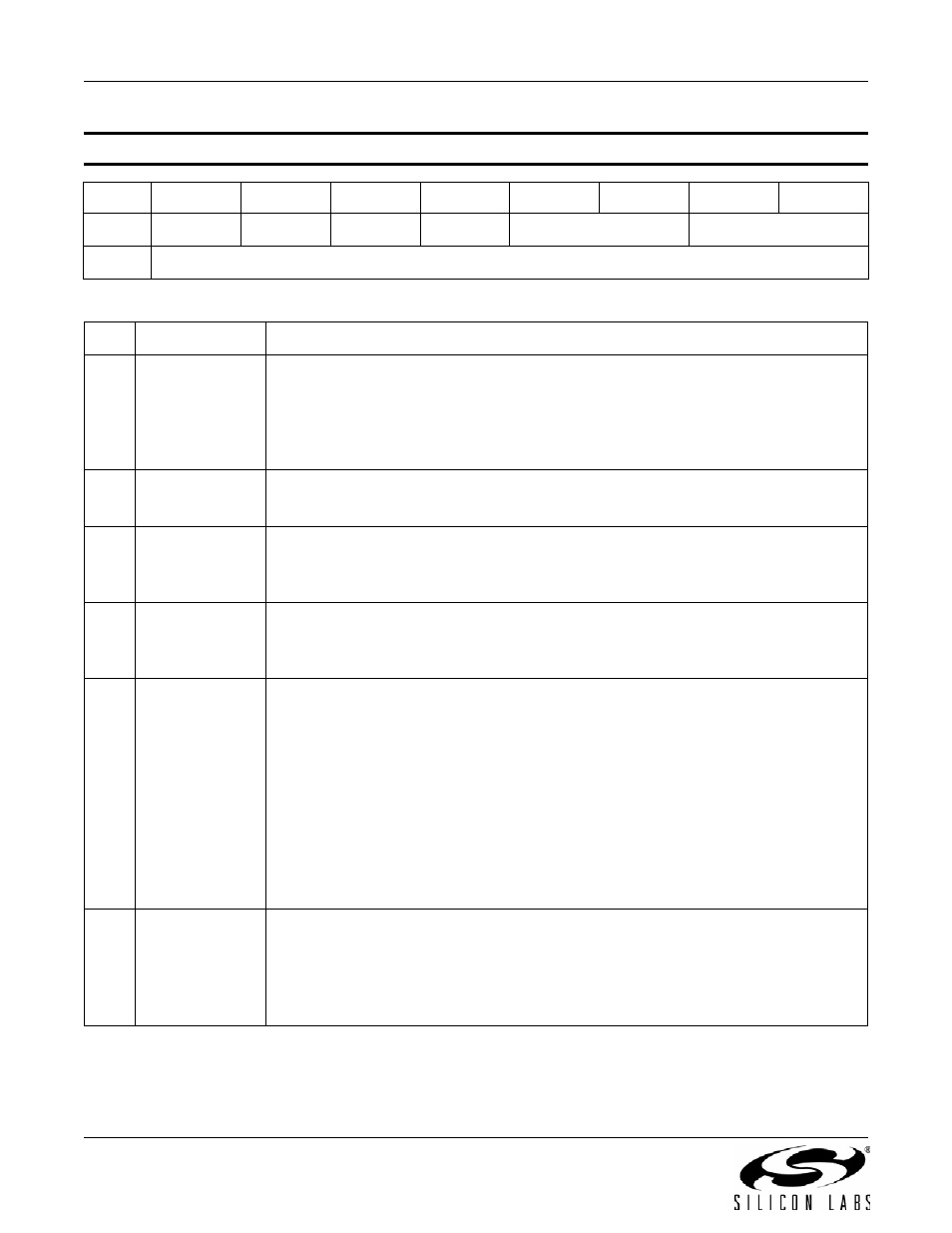

Reset value = 0000 0000

Register 22. CLK6 Control

Bit

D7

D6

D5

D4

D3

D2

D1

D0

Name

CLK6_PDN

FBA_INT

MS6_SRC

CLK6_INV

CLK6_SRC[1:0]

CLK6_IDRV[1:0]

Type

R/W

R/W

R/W

R/W

R/W

R/W

Bit

Name

Function

7

CLK6_PDN

Clock 7 Power Down.

This bit allows powering down the CLK6 output driver to conserve power when the out-

put is unused.

0: CLK6 is powered up.

1: CLK6 is powered down.

6

FBA_INT

FBA MultiSynth Integer Mode.

Set this bit according to ClockBuilder Desktop generated register map file.

5

MS6_SRC

MultiSynth Source Select for CLK6.

0: Select PLLA as the source for MultiSynth0.

1: Select PLLB (Si5351A/C only) or VCXO (Si5351B only) MultiSynth0.

4

CLK6_INV

Output Clock 6 Invert.

0: Output Clock 6 is not inverted.

1: Output Clock 6 is inverted.

3:2

CLK6_SRC[1:0]

Output Clock 0 Input Source.

These bits determine the input source for CLK6.

00: Select the XTAL as the clock source for CLK6. This option by-passes both synthe-

sis stages (PLL/VCXO & MultiSynth) and connects CLK6 directly to the oscillator

which generates an output frequency determined by the XTAL frequency.

01: Select CLKIN as the clock source for CLK6. This by-passes both synthesis stages

(PLL/VCXO & MultiSynth) and connects CLK6 directly to the CLKIN input. This essen-

tially creates a buffered output of the CLKIN input.

10: Reserved. Do not select this option.

11: Select MultiSynth 0 as the source for CLK6. Select this option when using the

Si5351 to generate free-running or synchronous clocks.

1:0

CLK6_IDRV[1:0] CLK6 Output Rise and Fall time / Drive Strength Control.

00: 2 mA

01: 4 mA

10: 6 mA

11: 8 mA