External clock with divider – Spectrum Brands MC.31XX User Manual

Page 61

Clock generation

External clocking

(c) Spectrum GmbH

61

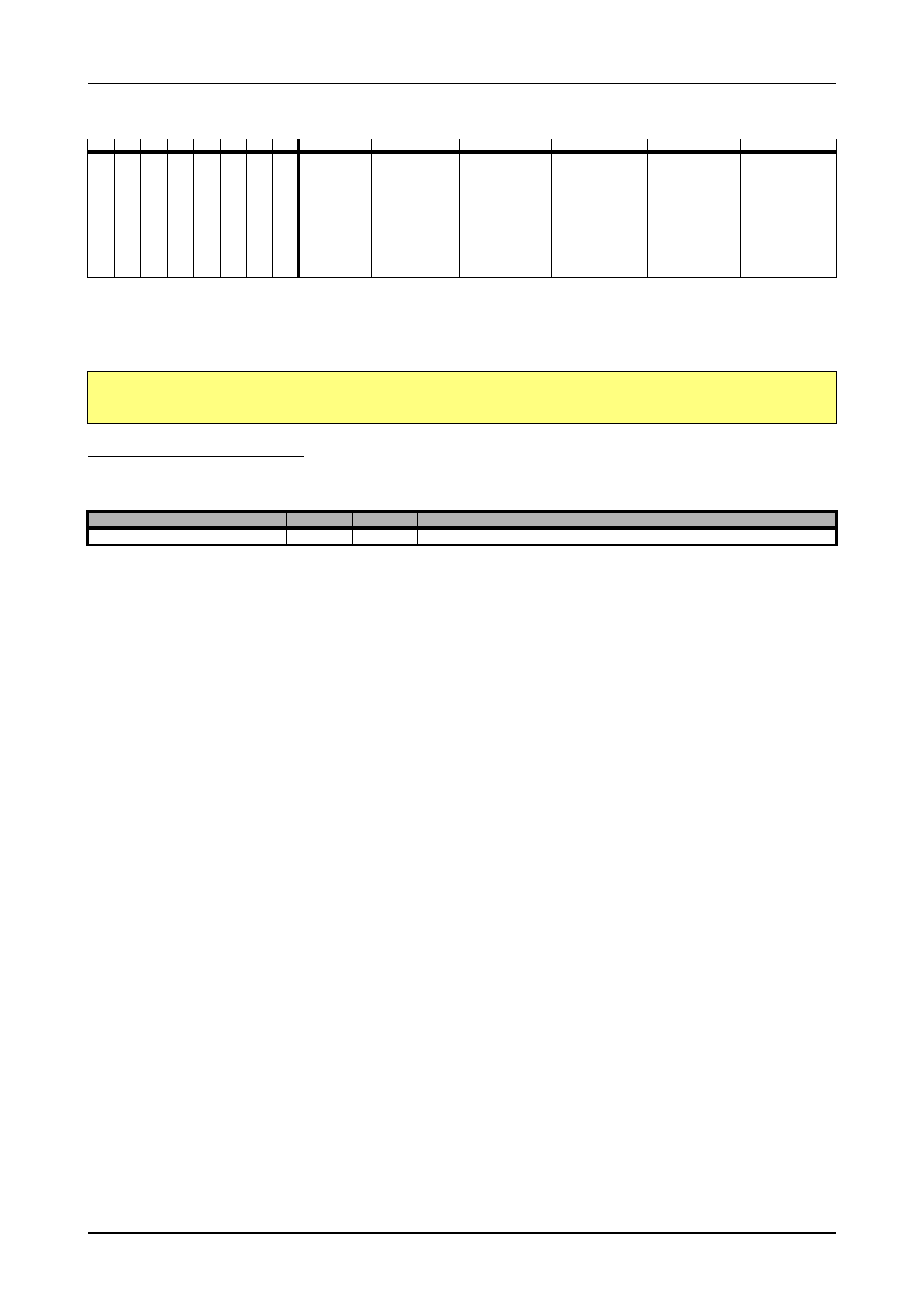

How to read this table? If you have activated all eight channels and are using the board in standard mode (not FIFO) and your external clock

is known to be around 15 MHz you have to set the EXRANGE_BURST_L for the external range.

Example:

External clock with divider

The extra clock divider can be used to divide an external fed in clock by a fixed value. The external clock must be > 1 MS/s. This divided

clock is used as a sample clock for the board.

Available divider values

ch0

ch1

ch2

ch3

ch4

ch5

ch6

ch7

Mode

EXRANGE_SINGLE EXRANGE_BURST_S EXRANGE_BURST_M EXRANGE_BURST_L

EXRANGE_BURST_XL

x

Standard/FIFO

< 5 MHz

5 MHz - max

x

x

Standard/FIFO

< 2.5 MHz

2.5 MHz - 7.5 MHz

7.5 MHz - 17.5 MHz 17.5 MHz - 36 MHz > 36 MHz

x

x

Standard

< 5 MHz

5 MHz - max

x

x

FIFO

< 2.5 MHz

2.5 MHz - 7.5 MHz

7.5 MHz - 17.5 MHz 17.5 MHz - 36 MHz > 36 MHz

x

x

x

x

Standard

< 2.5 MHz

2.5 MHz - 7.5 MHz

7.5 MHz - 17.5 MHz 17.5 MHz - 36 MHz > 36 MHz

x

x

x

x

FIFO

< 1.3 MHz

1.3 MHz - 3.8 MHz

3.8 MHz - 8.8 MHz

8.8 MHz - 18 MHz

> 18 MHz

x

x

x

x

Standard/FIFO

< 1.3 MHz

1.3 MHz - 3.8 MHz

3.8 MHz - 8.8 MHz

8.8 MHz - 18 MHz

> 18 MHz

x

x

x

x

x

x

x

x

Standard

< 1.3 MHz

1.3 MHz - 3.8 MHz

3.8 MHz - 8.8 MHz

8.8 MHz - 18 MHz

> 18 MHz

x

x

x

x

x

x

x

x

FIFO

< 0.7 MHz

0.7 MHz - 1.9 MHz

1.9 MHz - 4.4 MHz

4.4 MHz - 9 MHz

> 9 MHz

SpcSetParam (hDrv, SPC_CHENABLE, CHANNEL0 | CHANNEL1 | CHANNEL2 | CHANNEL3); // activate 4 channels

SpcSetParam (hDrv, SPC_EXTERNALCLOCK, 1); // activate external clock

SpcSetParam (hDrv, SPC_EXTERNRANGE, EXRANGE_BURST_M); // set external range to Burst M

Register

Value

Direction

Description

SPC_CLOCKDIV

20040

r/w

Extra clock divider for external samplerate. Allowed values are listed below

1

2

4

8

10

16

20

40

50

80

100

200

400

500

800

1000

2000