Datasheet – SMSC USB97C242 User Manual

Page 14

USB 2.0 Flash Drive Controller

Datasheet

SMSC USB97C242

Page 14

Revision 1.4 (05-03-07)

DATASHEET

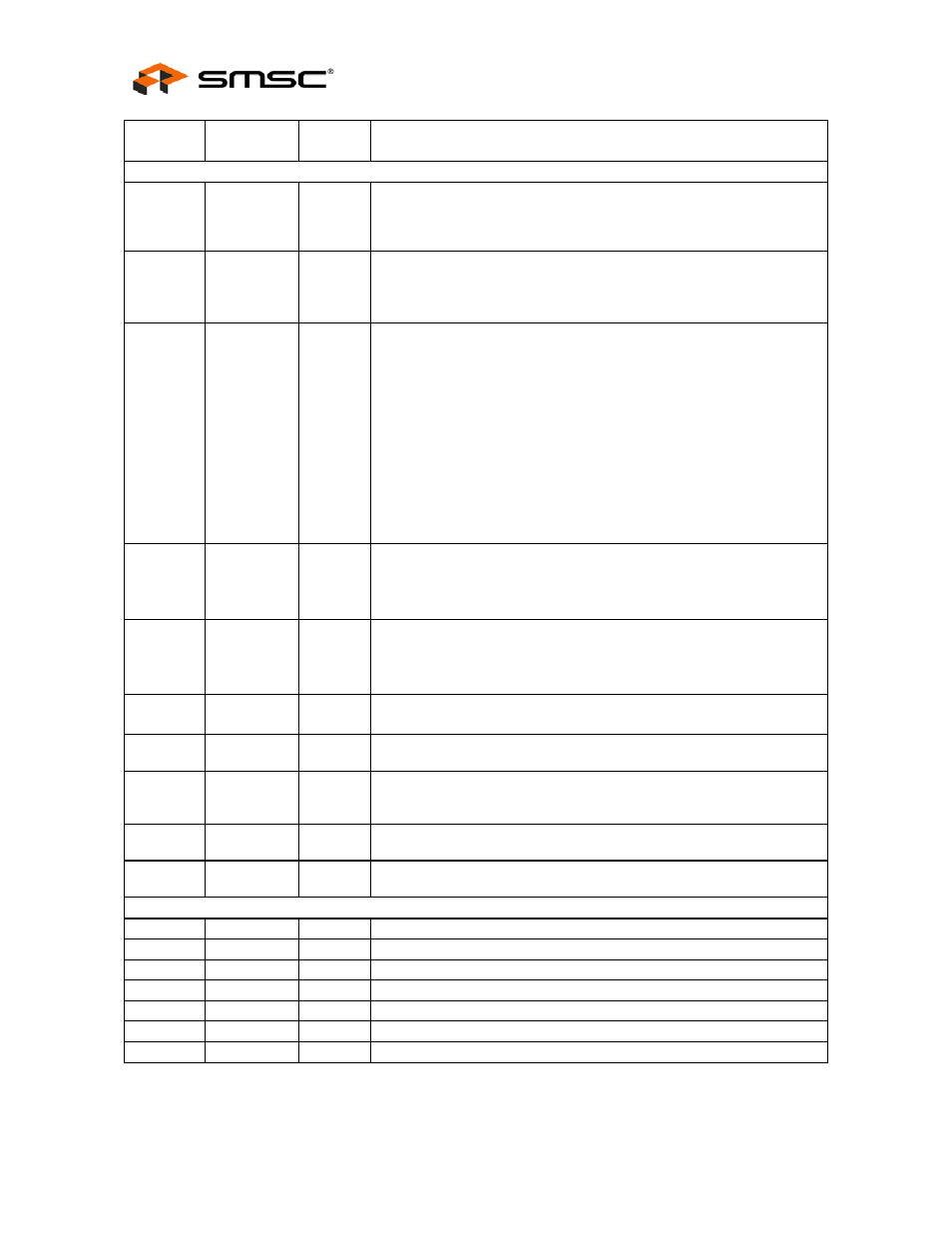

NAME

SYMBOL

BUFFER

TYPE

DESCRIPTION

MISC

Crystal

Input/Extern

al Clock

Input

XTAL1/

CLKIN

ICLKx

12Mhz Crystal or external clock input.

This pin can be connected to one terminal of the crystal or can be

connected to an external 12Mhz clock when a crystal is not used.

Crystal

Output

XTAL2 OCLKx

12Mhz

Crystal

This is the other terminal of the crystal, or left open when an external

clock source is used to drive XTAL1/CLKIN. It may not be used to drive

any external circuitry other than the crystal circuit.

Internal

ROMEN

ROMEN

IPU

When tied low, an external program memory should be connected to the

memory/data bus. The USB97C242 uses this external bus for program

execution.

When this pin is left unconnected or tied high, the USB97C242 uses the

internal ROM for program execution.

The state of this pin is latched internally on the rising edge of nRESET to

determine if internal or external program memory is used.

The state latched is stored in ROMEN bit of GPIO_IN1 register.

General

Purpose I/O

GPIO1

I/O8

This pin may be used either as input, edge sensitive interrupt input, or

output. See Chapter 11 for usage by program in internal ROM.

General

Purpose I/O

GPIO2

I/OPU8 This pin may be used either as input, edge sensitive interrupt input, or

output. See Chapter 11 for usage by program in internal ROM.

General

Purpose I/O

GPIO3

I/O8

This pin may be used either as input, edge sensitive interrupt input, or

output. See Chapter 11 for usage by program in internal ROM.

General

Purpose I/O

GPIO[7:4]

I/O8

These pins may be used either as input, edge sensitive interrupt input, or

output. See Chapter 11 for usage by program in internal ROM.

NAND flash

Chip Select

Signal

nCS[7:0]

OPU8

These pins can be used to chip enable the NAND flash devices, when

multiple NAND flash devices are used.

RESET

input

nRESET

IS

This active low signal is used by the system to reset the chip. The active

low pulse should be at least 100ns wide.

TEST Input nTEST[0:1]

I

These signals are used for testing the chip. User should normally leave

them unconnected.

POWER, GROUNDS, AND NO CONNECTS

VDD

+2.5V Core power

VDDIO

+3.3V I/O power

VDDP

+2.5 Analog power

VSSP

Analog Ground Reference

VDDA

+3.3V Analog power

VSSA

Analog Ground Reference

GND

Ground

Reference