Chapter 5 block diagram, Datasheet – SMSC USB97C242 User Manual

Page 11

USB 2.0 Flash Drive Controller

Datasheet

SMSC USB97C242

Page 11

Revision 1.4 (05-03-07)

DATASHEET

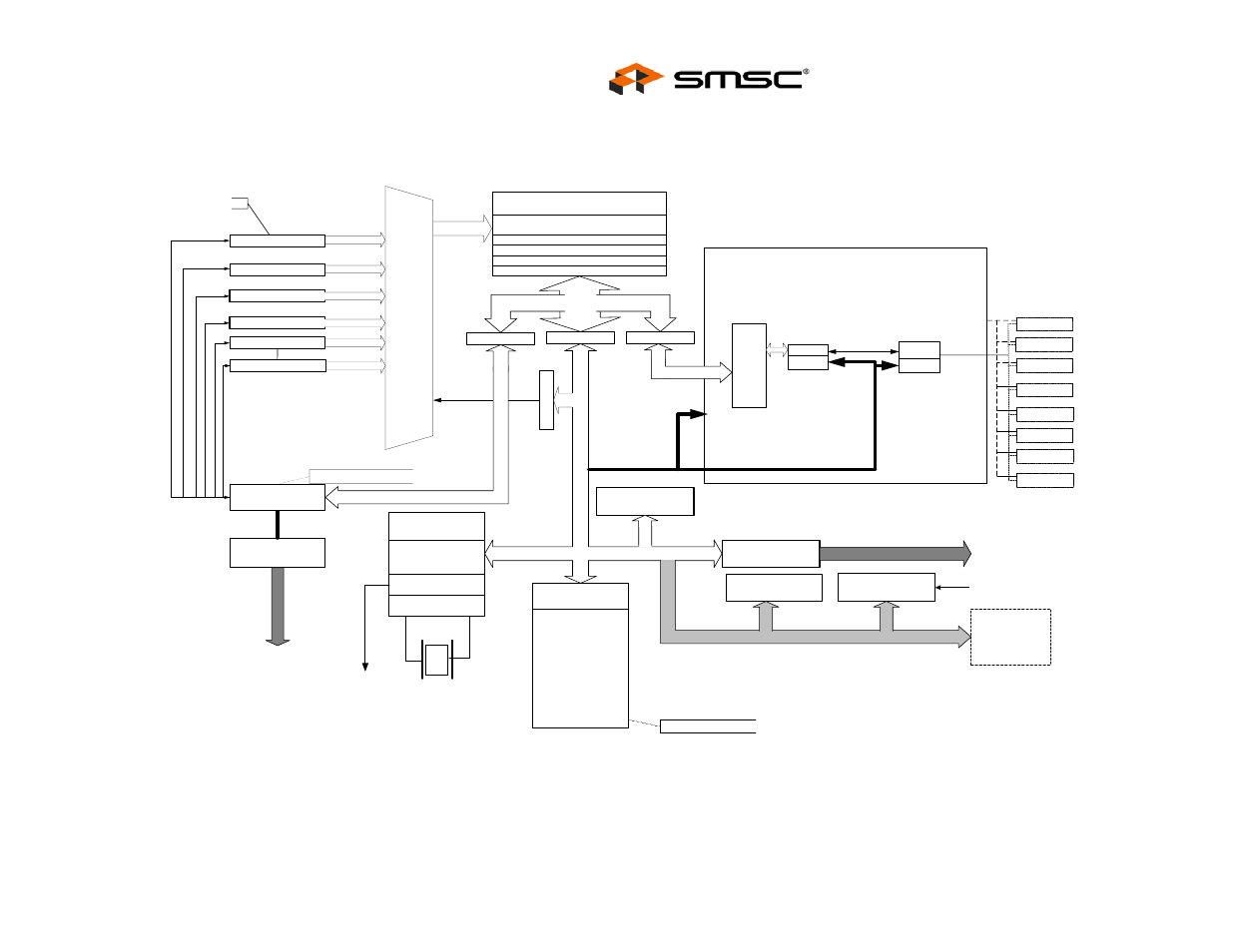

Chapter 5 Block Diagram

Flash

M edia

D M A

U nit

D

a

ta

B

u

s

s

U S B 2.0 P HY

( T ransciever )

FAS T 8051

C P U C O R E

G P IO

7 pins

7 pins

Co n fig u ratio n an d C on trol

C lo ck G en eratio n

XTA

L

S IE

( S erial Interface E ngine )

P rogram M em ory/ IO

B us

Interrup t Co n tro ller

L atch p h ase 0, 2

S IE

L atch p hase 3

8051

L atch ph ase 1

F M C

60M H z

32 B it

O sc

A ddress

X

D

AT

A &

SF

R

A

d

d

ress

an

d D

a

ta

buss

e

s

64 B ytes E P 0T X

64 B ytes E P 0RX

64 B ytes E P 1T X

64 B ytes E P 1RX

A uto address generators

A

d

dress

M

U

X

D ata @ 32 bit

15M hz

S IE C on trol Reg s

A ddress

A ddress

A ddress

A ddress

E P 0RX_B C

R A M RD _A /B

E P 0T X_B C

R A M W R_A /B

32 bit 15M Hz Data B uss

C LO CK O U T

12 M H z

512 B ytes E P 2 T X/RX B uffer A

Ad

d

re

ss Reg

iste

r

1.25K B

S R AM

12K B yte

S cratchpad

S R A M

C locked byP hase 0, 2 C lock

Clocked by P hase 3 Clock

512 B ytes E P 2 T X/RX B uffer B

M em ory

C ards

S cratchpad

S R A M (768 B yte)

E C C

C ontrol/

S tatus

Flash M edia

C ontroller (F M C )

S M

Controller

N A N D F lash

C ontrol/

S tatus

M E M /IO B us 29pins

DA TA

E P 1T X_B C

E P 1R X_B C

A ddress

A ddress

NA N D F lash

S M /

N A N D F lash

N A N D F lash

C S [7:0]

48K B RO M

R O M E N

N A N D F lash

N A N D F lash

N A N D F lash

N A N D F lash