1 memory subsystem, Table 2. supported dimm module types, 2 dimm placement ddr2 400 – Intel Xeon User Manual

Page 11: Table 3. dimm placement ddr2 400, Memory subsystem, Dimm placement ddr2 400, Supported dimm module types

Intel

®

Xeon™ Processor, Intel

®

E7520 Chipset, Intel

®

6300ESB ICH Development Kit User’s Manual

11

Product Overview

1.4.1

Memory Subsystem

The memory subsystem is designed to support Double Data Rate2(DDR2) Synchronous Dynamic

Random Access Memory (SDRAM) using the Intel(R) E7520 MCH. The MCH provides two

independent DDR channels, which support DDR2 400 DIMMs. The peak bandwidth of each

DDR2 branch channel is 3.2 Gbyte/s (8 bytes x 400 MT/s) with DDR2 400. The two DDR2

channels from the MCH operate in lock step; the effective overall peak bandwidth of the DDR2

memory subsystem is 6.4 Gbyte/s for DDR2 400.

shows all DIMM technology supported by the CRB. Other DIMM types are not supported.

1.4.2

DIMM Placement DDR2 400

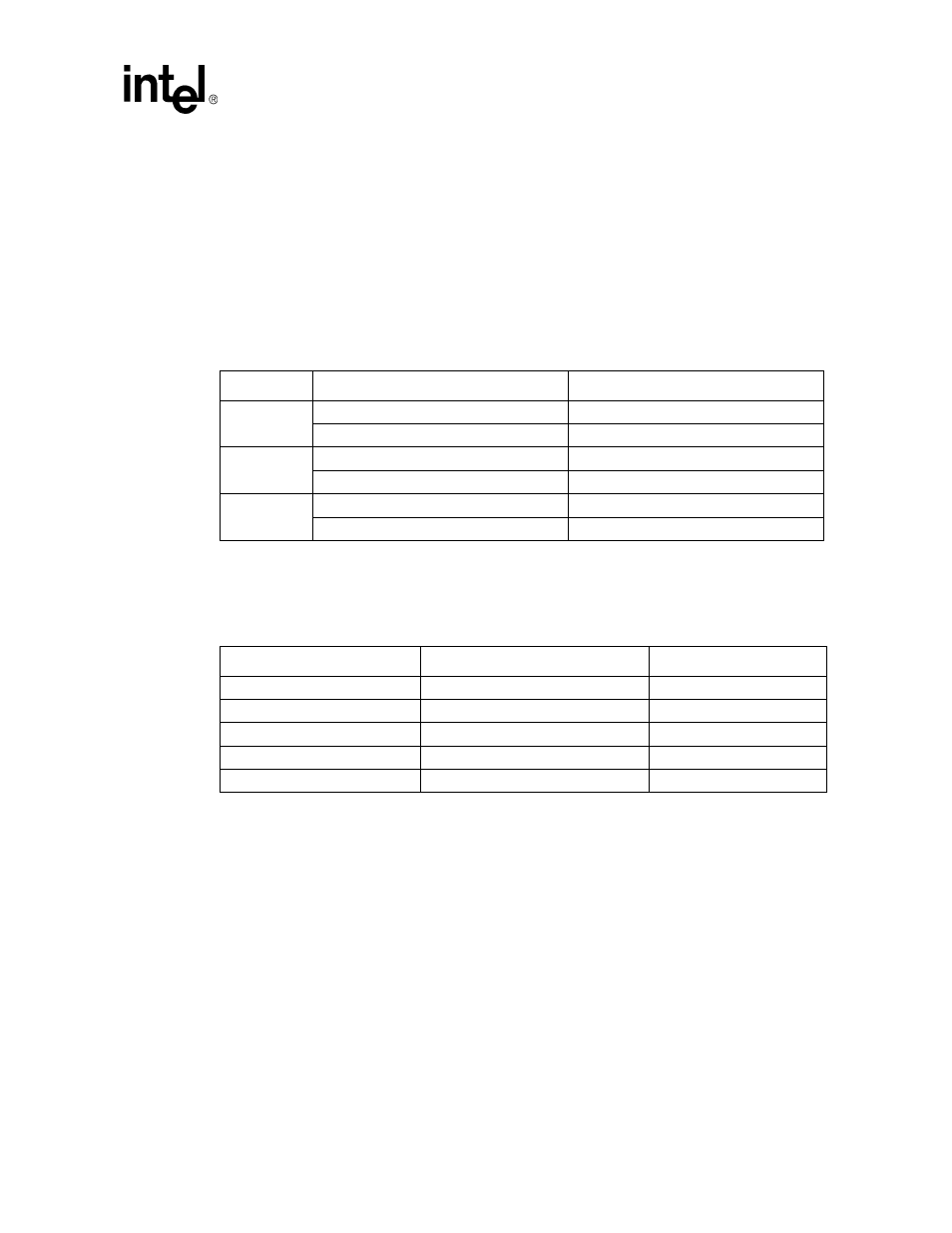

Table 2.

Supported DIMM Module Types

Technology

Organization

SDRAM Chips/DIMM

256 Mbit

8 Mbytes x 8 x 4 banks

8

16 Mbytes x 4 x 4 banks

16

512 Mbit

16 Mbytes x 8 x 4 banks

8

32 Mbytes x 4 x 4 banks

16

1 Gbit

32 Mbytes x 8 x 4 banks

8

64 Mbytes x 4 x 4 banks

16

Table 3.

DIMM Placement DDR2 400

DIMM Configuration

DIMM1

DIMM2

1 Single Rank

Empty

Single Rank

1 Dual Rank

Empty

Dual Rank

2 Single Rank

Single Rank

Single Rank

1 Dual Rank, 1 Single Rank

Single Rank

Dual Rank

2 Dual Rank

Dual Rank

Dual Rank

NOTES:

1. Populate DIMMs starting with the sockets farthest away from the MCH (DIMM slots A2 and B2).

2. When populating both channels, always place identical DIMMs in sockets that have the same position on

channel A and channel B (i.e., DIMM A2 should be identical to DIMM B2).