Motorola VL-RISC MCF5202 User Manual

Page 9

MOTOROLA

GATEWAY BOARD

9

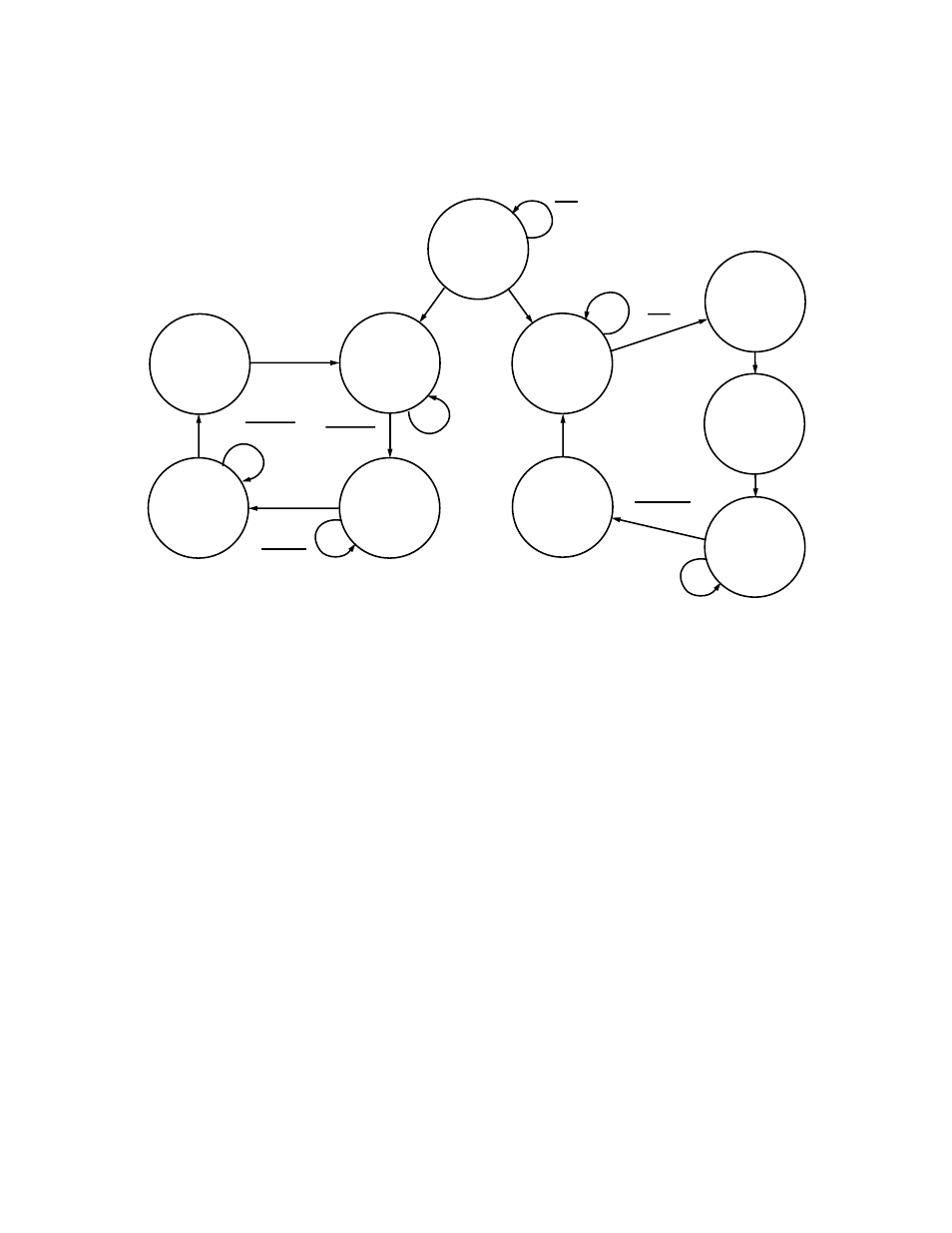

7.0 PLD State Diagram

Figure 4: SimpliÞed PLD State Diagram

8.0 PLD ABEL Code

MODULE gateway

TITLE 'The controlling signals between a 5202 and a 68EC000'

gateway device 'ispLSI';

pLSI property 'PART ispLSI1016-80LT44';

pLSI property 'IGNORE_FIXED_PIN OFF';

pLSI property 'PULLUP ON';

pLSI property 'Y1_AS_RESET ON';

pLSI property 'LOCK AVEC

1';

pLSI property 'LOCK HALT

2';

pLSI property 'LOCK PCLK

5';

"pLSI property 'LOCK SDI

8';

pLSI property 'LOCK TT1

9';

pLSI property 'LOCK TT0

10';

pLSI property 'LOCK ATM

11';

pLSI property 'LOCK BR68K

15';

"pLSI property 'LOCK SDO

18';

pLSI property 'LOCK SIZ1

19';

pLSI property 'LOCK BDCF

21';

"pLSI property 'LOCK SCLK

27';

"pLSI property 'LOCK RSTI

29';

Reset

Wait

for

beginning

of ColdFire

cycle

Begin a

68EC000

cycle

Data

Acknowledge

to the

MCF5202

Wait

for

Acknowledge

from

68EC000

TS

TS

TS

TS

DTACK

DTACK

Grant to

ColdFire

Grant to

68EC000

No

Grant

BDCF

BDCF

No

Grant

BR68K

BR68K

BR68K

BR68K

Bus Master

Assert

other control

signals

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

.

..