Motorola VL-RISC MCF5202 User Manual

Page 5

MOTOROLA

GATEWAY BOARD

5

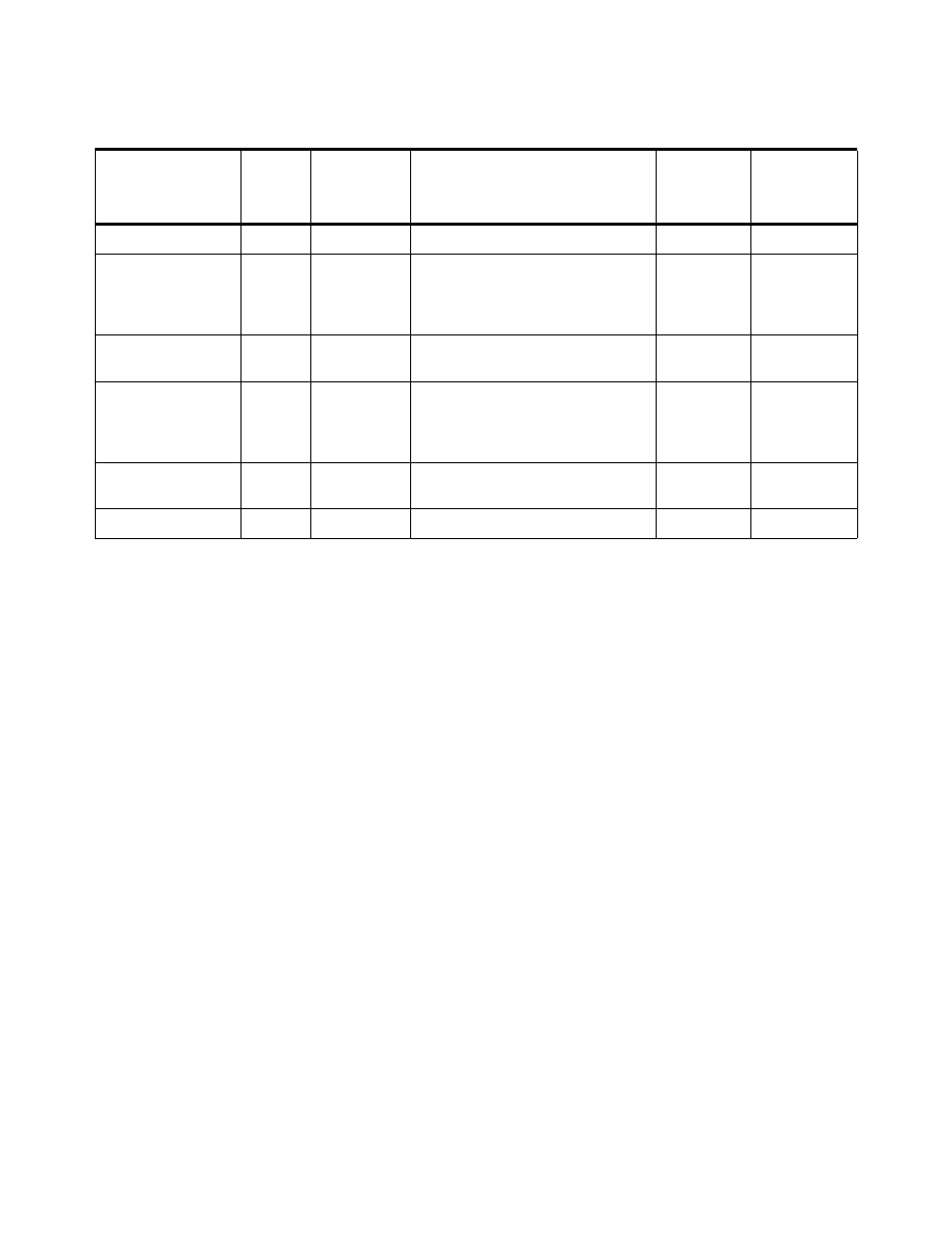

Table 4: Dhrystone 2.1 Benchmark Performance

4.0 Potential Performance and System Improvements

To fully take advantage of the MCF5202 performance in a target system, the 68EC000 bus could be changed to

interface better to the MCF5202 bus. First, the maximum frequency of operation for the Gateway boardÕs MCF5202

is 33MHz, which can be a substantial improvement over the 12.5MHz, 16.7MHz, or even the 20MHz version of the

68EC000. So, if the 68EC000 system was designed to operate at higher frequencies, this would be an easy way to

increase overall system performance. Second, the 16-bit 68EC000 data bus could be widened to 32-bits so that the

MCF5202 can get a longword in one bus transaction instead of the two bus transactions that are required now through

the Gateway board. Three, when the MCF5202 does a burst access (gives one address, expects 4 longwords of data),

if the 68EC000 system could be changed to provide the secondary 3 longwords faster than the full bus transaction

required by the current 68EC000 system, the overall MCF5202 performance can be improved dramatically. For

example, if the data bus was widened to 32-bits and page mode DRAM was used in the system, the MCF5202 could

potentially do a cache line Þll (4 longwords) in 7 bus clocks (4-1-1-1) instead of 49 bus clocks (6-6-6-6-6-6-6-7).

The MCF5202 was chosen for the Gateway board because of its on-chip 2KB uniÞed cache that allows custom-

ers to experiment among various on-chip memory conÞgurations. For example, the 2KB uniÞed cache can be conÞg-

ured to be 2KB of I-cache only, 2KB of D-cache only, 1KB of I-cache and 1KB of D-cache, or as a normal 2KB

uniÞed cache with a dynamic mixture of both instructions and data. Other ColdFire microprocessors can be selected

according to speciÞc system requirements. For example, the MCF5204, which would not require latches and buffers

because it has a demultiplexed address and data bus (just like the 68EC000) has a little less on-chip memory (512

byte I-cache and 512 byte SRAM) compared to the MCF5202. Therefore, using the MCF5204 would most likely

give a little less performance, but would save overall system cost.

5.0 Debug Support

There is a ColdFire BDM connector (labeled J2) on the Gateway board that is a 26-pin Berg Connector

arranged in two rows of thirteen pins each. This connector is commonly used by software debugger vendors to allow

such features as real-time trace, real-time debug, and background debug.

SYSTEM

DATA

WIDTH

FREQUENCY

DRAM ACCESSES

(TO GET 16 BYTES)

CACHE

MODE

MIPS

(@ GIVEN

FREQUENCY)

MC68EC000 Board

16 bit

12.5 MHz

8-8-8-8-8-8-8-8

N/A

1.01

Gateway Board

8 bit

20 MHz

R: 10-10-10-11-10-10-10-11-

10-10-10-11-10-10-10-11

W: 9- 9- 9-11- 9- 9- 9-11-

9- 9- 9-11- 9- 9- 9-11

Off

0.56

Gateway Board

16 bit

20 MHz

R: 10-11-10-11-10-11-10-11

W: 9-11- 9-11- 9-11- 9-11

Off

1.07

Gateway Board

8 bit

20 MHz

R: 10-10-10-10-10-10-10-10-

10-10-10-10-10-10-10-11

W: 9- 9- 9- 9- 9- 9- 9- 9-

9- 9- 9- 9- 9- 9- 9-11

Copy-Back

5.95

Gateway Board

16 bit

20 MHz

R: 10-10-10-10-10-10-10-11

W: 9- 9- 9- 9- 9- 9- 9-11

Copy-Back

9.12

MCF5202 Board

32 bit

20 MHz

8-4-4-4

Copy-Back

12.6

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

.

..