Motorola VL-RISC MCF5202 User Manual

Page 2

2

GATEWAY BOARD

MOTOROLA

2.1.1 Mapping 32-bit MCF5202 addresses to 24-bit 68EC000 addresses

The Gateway board transfers only the lower 24-bits of the address from the MCF5202 to the MC68EC000.

This should make no difference in porting the system software (because a 24-bit addressing scheme can still be used,

with the upper 8-bits as a ÒdonÕt-careÒ) except when the on-chip cache is to be used. The MCF5202 allows speciÞc

regions of address space to be assigned access control attributes via the Access Control Registers (ACR0 and ACR1).

Also, within the MCF5202Õs Cache Control Register (CACR), the default cache mode can be set up for regions that

are not mapped by the ACRs. Refer to the ÒCacheÓ section of the

ColdFire MCF5202 UserÕs Manual

for more

details. The MCF5202 ACRs use address bits 31-24 to determine the region of space to which the corresponding

access control attributes are assigned. Because the original M68000 system used only addresses 23-0, this at Þrst

glance may seem to cause a problem when considering caching certain areas of memory that are smaller than

16Mbytes. However, virtual-to-physical memory mapping can be used to map unique regions in the 24-bit address

space to unique 16Mbyte regions in the 32-bit address space, such that certain areas of the physical memory map can

take advantage of the MCF5202 caching schemes. One example of implementing this would be to simply concate-

nate A[31:24] = $01 in front of the Þrst 24-bit address region, and control the caching scheme for this region using

ACR0. Then concatenate A[31:24] = $02 in front of the second 24-bit address region, which will have a separate

caching scheme, and control the caching scheme for this region with ACR1. Finally, concatenate A[31:24] = $03 in

front of the third 24-bit address region, which could have yet another caching scheme, and control the caching

scheme for this region using the default cache mode in the CACR register. This example memory map translation is

shown in Table 1.

For this example, ACR0 can be set up such that everything within the region $01xxxxxx, which includes

$01000000 - $011FFFFF containing instructions, can have a speciÞc cache attribute such as copyback. ACR1 can be

set up such that everything within the region $02xxxxxx, which includes $02200000 - $023FFFFF containing data,

can have another speciÞc cache attribute such as writethrough. The CACR can be set up such that everything not

mapped by the ACRs, which includes $03400000 - $03FFFFFF containing I/O, can have a third cache attribute such

as cache inhibit. Now, when the software code is compiled, the new MCF5202 memory map that is speciÞc to the

customerÕs system must be used when assigning the corresponding instruction, data, and I/O sections.

2.1.2 Cache Coherency

If the MCF5202 has its cache on and in copyback mode, and if there is another bus master in the system that

can arbitrate the system bus away from the MCF5202 and modify a shared piece of memory, users should be careful

about maintaining cache coherency. Cache coherency is the term used to describe the act of keeping the on-chip

cache consistent (or coherent) with external memory, if other masters will be using the same memory. Refer to the

ÒCache CoherencyÓ section of the

ColdFire MCF5202 UserÕs Manual

. If cache coherency is required, then the sim-

plest way to resolve this problem is to control the shared memory region with one of the ACRs and set this ACRÕs

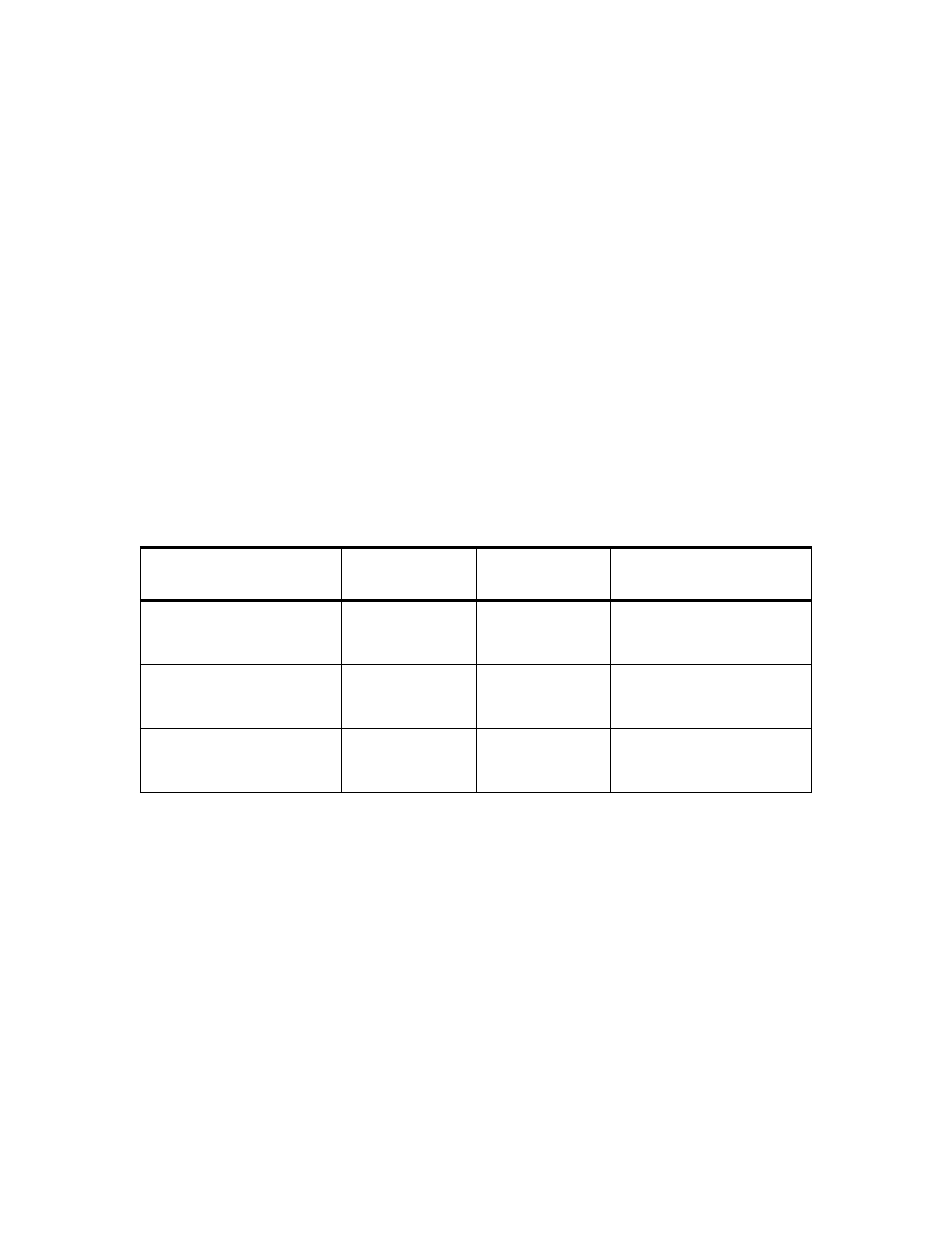

Table 1: Example Memory Map Translation

68000 MEMORY MAP

A[23:0]

CONTENTS

CACHE CONTROL

5202 MEMORY MAP

A[31:0]

$000000

$1FFFFF

Instructions

ACR0

$01000000

$011FFFFF

$200000

$3FFFFF

Data

ACR1

$02200000

$023FFFFF

$400000

$FFFFFF

I/O

CACR

$03400000

$03FFFFFF

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

.

..