0 bus operation, Freescale semiconductor, inc – Motorola VL-RISC MCF5202 User Manual

Page 6

6

GATEWAY BOARD

MOTOROLA

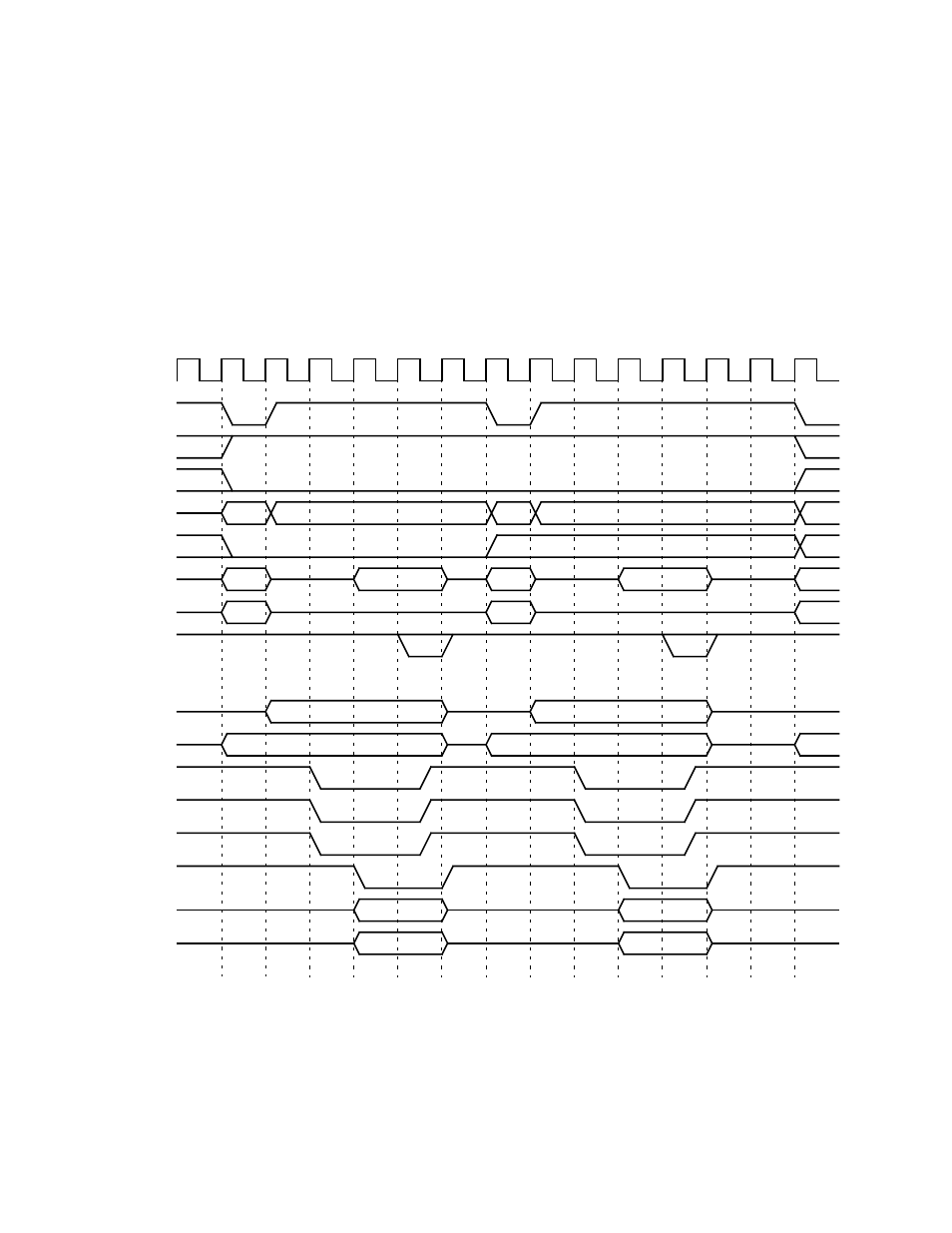

6.0 Bus Operation

The Gateway board supports a synchronous interface between the MCF5202 bus and the MC68EC000 bus.

The waveforms in this document are meant to provide a functional description of the bus cycles required for data

transfer operations. The examples below show a longword read and write to a 16-bit wide data bus of the

MC68EC000 as well as an Interrupt Acknowledge Cycle. Note that at all times the MCF5202 will not burst

(TBI*=0) and that the address phase lasts for only one clock (AA*=0).

Figure 1: Longword Read To A 16-Bit Port

AD[31:16]

CLOCK

READ D[31:16]

ADDR

00

ADDR

ADDR

ADDR

READ D[15:0]

00

01

01

10

READ D[31:24]

READ D[23:16]

READ D[15:8]

READ D[7:0]

TS*

R/W*

TT[1:0]

ATM

SIZ[1:0]

AD[15:0]

DA*[1:0]

FC[2:0]

A[23:0]

AS*

UDS

LDS

DTACK*

D[15:8]

D[7:0]

w

S0

S2

S4

S6

w

w

PS1

w

PS1

PS2

PS3

PS4

PS5

PS1

PS1

S0

S2

S4

S6

w

w

PS2

PS3

PS4

PS5

PS1

PS1

w

PS1

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

.

..