Motorola VL-RISC MCF5202 User Manual

Page 4

4

GATEWAY BOARD

MOTOROLA

The industry standard Dhrystone 2.1 benchmark was run on the Motorola Gateway board, as well as some other

systems, and the results are shown in Table 4. If you notice in Table 4, the Gateway board requires about a 7.5MHz

increase in frequency (12.5MHz to 20MHz) to get about the same MIPS performance of the 68EC000 evaluation

board. This is attributable to the handshaking required between the MCF5202 and the 68EC000. Notice, however, if

the internal cache of the MCF5202 is used, the MIPS performance of the system is increased dramaticallyÑmore

than 8 times better than with cache off. In addition, if system bus interface changes are made to take advantage of the

MCF5202 bus interface, such as widening the data bus and allowing bursting (which will be discussed later), even

greater system performance will result.

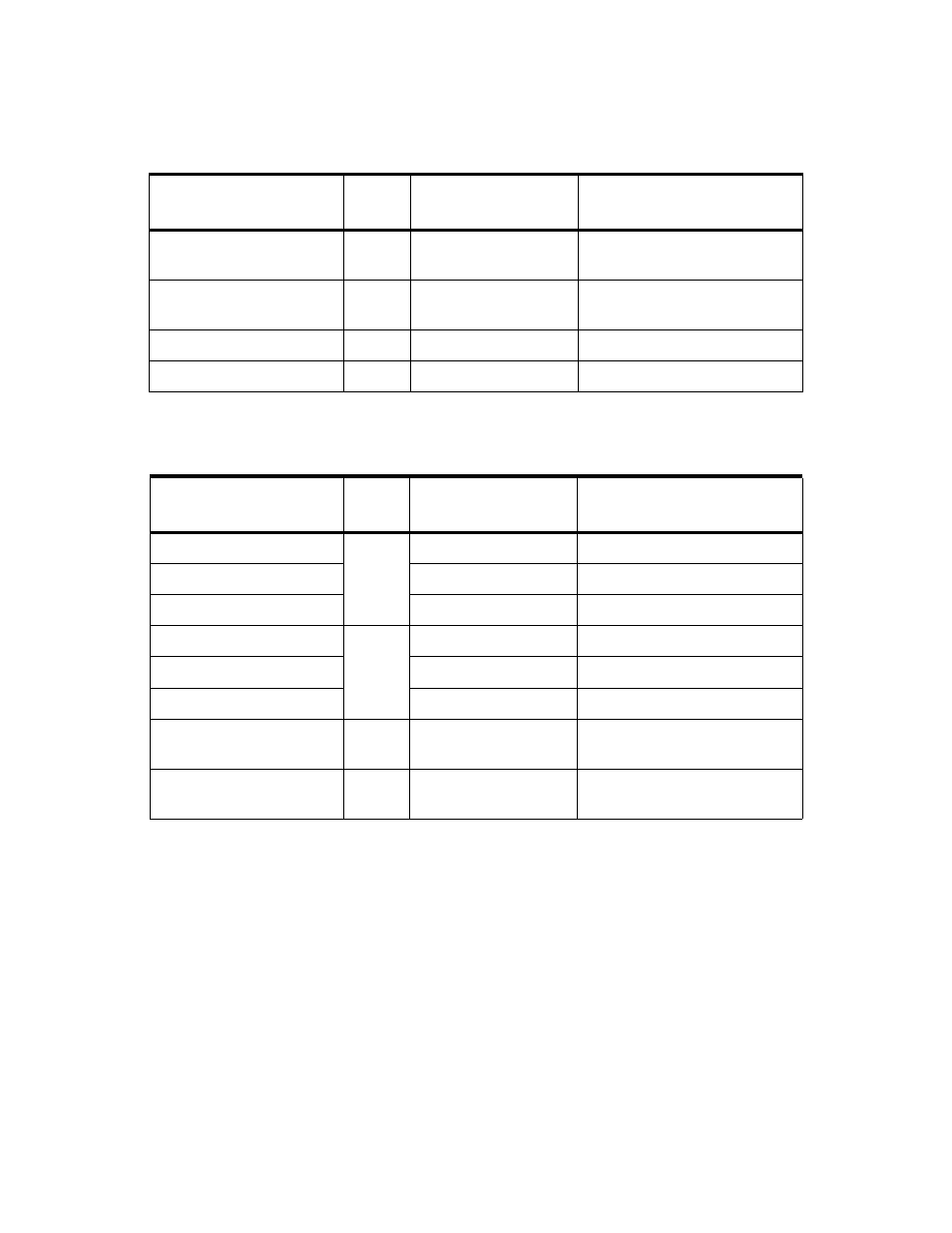

Table 2: Bus Clock Timing Comparison (16-bit mode)

MCF5202 DATA ACCESS

READ/

WRITE

GATEWAY BOARD

BUS CLOCKS

EQUIVALENT MC68EC000 BUS

CLOCKS TO GET SAME DATA

Byte, Word

Long

Read

7

6+7=13

4

4+4=8

Byte, Word

Long

Write

7

5+7=12

4

4+4=8

Line Fill (4 Longs)

Read

6+6+6+6+6+6+6+7=49

4+4+4+4+4+4+4+4=32

Line Fill (4 Longs)

Write

5+5+5+5+5+5+5+7=42

4+4+4+4+4+4+4+4=32

Table 3: Bus Clock Timing Comparison (8-bit mode)

MCF5202 DATA ACCESS

READ/

WRITE

GATEWAY BOARD

BUS CLOCKS

EQUIVALENT MC68EC000 BUS

CLOCKS TO GET SAME DATA

Byte

Read

7

4

Word

6+7=13

4+4=8

Long

6+6+6+7=25

4+4+4+4=16

Byte

Write

7

4

Word

5+7=12

4+4=8

Long

5+5+5+7=22

4+4+4+4=16

Line Fill (4 Longs)

Read

6+6+6+6+6+6+6+6+

6+6+6+6+6+6+6+7=97

4+4+4+4+4+4+4+4+

4+4+4+4+4+4+4+4=64

Line Fill (4 Longs

Write

5+5+5+5+5+5+5+5+

5+5+5+5+5+5+5+7=82

4+4+4+4+4+4+4+4+

4+4+4+4+4+4+4+4=64

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

.

..