14 mii speed control register (mii_speed), Figure614 . mii_speed register, Table615 . mii_speed field descriptions – Freescale Semiconductor POWERPC MPC860T User Manual

Page 46: Mii speed control register (mii_speed) -14, Mii_speed register -14, Mii_speed field descriptions -14, Freescale semiconductor, inc

6-14

MPC860T (Rev. D) Fast Ethernet Controller Supplement

MOTOROLA

PRELIMINARYÑSUBJECT TO CHANGE WITHOUT NOTICE

completes. At this time the contents of MII_DATA match the original value written except

for the DATA Þeld, whose contents have been replaced by the value read from the PHY

register.

Writing to MII_DATA during frame generation alters the frame contents. Software should

use the MII_DATAIO_COMPL interrupt to avoid writing to the MII_DATA register during

frame generation.

6.2.14 MII Speed Control Register (MII_SPEED)

The MII_SPEED register, shown in Figure 6-14, provides control of the MII clock (MDC

pin) frequency and allows the MII management frame preamble to be dropped.

MII_SPEED is written by the user.

Table 6-15 describes MII_SPEED Þelds.

The MII_SPEED Þeld must be programmed with a value to provide an MDC frequency of

less than or equal to 2.5 MHz to comply with the IEEE MII speciÞcation. MII_SPEED must

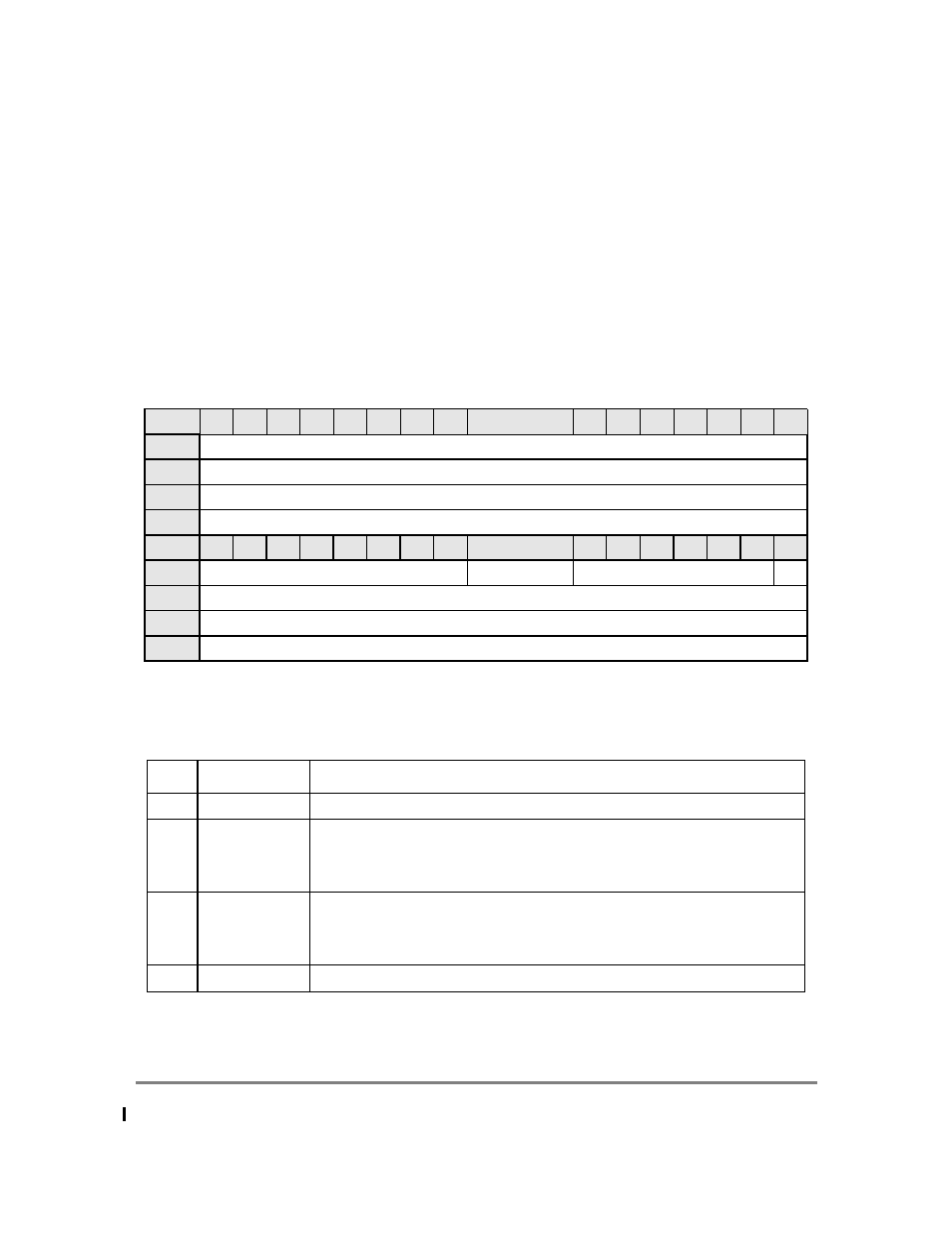

Bits

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Field

Ñ

Reset

0000_0000_0000_0000

R/W

Read/write

Addr

0xE84

Bits

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Field

Ñ

DIS_PREAMBLE

MII_SPEED

Ñ

Reset

0000_0000_0000_0000

R/W

Read/write

Addr

0xE86

Figure 6-14. MII_SPEED Register

Table 6-15. MII_SPEED Field Descriptions

Bits

Name

Description

0Р23

С

Reserved. Should be written to zero by the host processor.

24

DIS_PREAMBLE

Discard preamble. The MII standard allows the preamble to be dropped if the attached

PHY devices does not require it.

0 Preamble is not discarded.

1 Causes the preamble (32 1s) not to be prepended to the MII management frame.

25Ð30

MII_SPEED

MII_SPEED controls the frequency of the MII management interface clock (MDC)

relative to system clock. Clearing MII_SPEED, turns off the MDC and leaves it in

low-voltage state. Any non-zero value generates an MDC frequency of

1/(MII_SPEED*2) of the system clock frequency.

31

Ñ

Reserved. Should be written to zero by the host processor.

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

.

..