Table610 . i_event/i_mask field descriptions, 10 ethernet interrupt vector register (ivec), Ethernet interrupt vector register (ivec) -9 – Freescale Semiconductor POWERPC MPC860T User Manual

Page 41: I_event/i_mask field descriptions -9

MOTOROLA

Chapter 6. Programming Model

6-9

PRELIMINARYÑSUBJECT TO CHANGE WITHOUT NOTICE

and RFINT to notify at the end of frame.

6.2.10 Ethernet Interrupt Vector Register (IVEC)

The Ethernet interrupt vector register (IVEC), shown in Table 6-11, indicates the class of

interrupt generated by the FEC (IVEC) and provides control of the interrupt level

(ILEVEL).

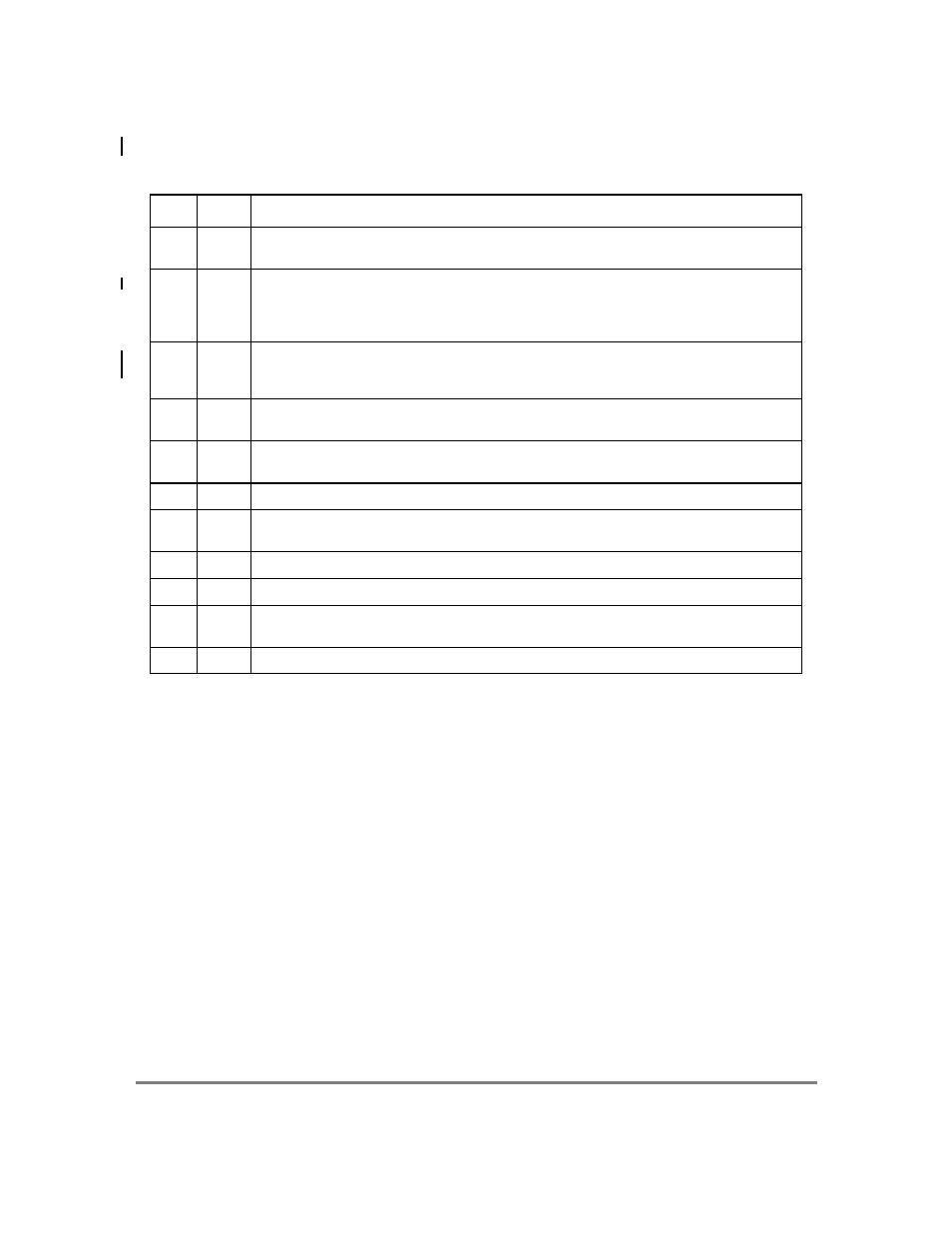

Table 6-10. I_EVENT/I_MASK Field Descriptions

Bits

Name

Description

0

HBERR Heartbeat error. When I_EVENT[HBC] is set, this interrupt indicates that heartbeat was not

detected within the heartbeat window following a transmission.

1

BABR

Babbling receive error. Indicates a received frame exceeded MAX_FRAME_LENGTH bytes. The

hardware truncates receive frames exceeding 2047 bytes so as not to overßow receive buffers.

Note that the Þrst revision of the MPC860T (mask #H56S) must not be given frames in excess of

2047 as it does not truncate frames.

2

BABT

Babbling transmit error. Indicates that the transmitted frame exceeded MAX_FRAME_LENGTH

bytes. This condition is usually caused by too large a a frame being placed into the transmit data

buffers. The transmit frame is not truncated.

3

GRA

Graceful stop complete. A graceful stop initiated by the setting of GTS is complete. GRA is set

when the transmitter Þnishes sending any frame that was in progress when GTS was set.

4

TFINT

Transmit frame interrupt. Indicates that a frame was sent and that the last corresponding BD was

updated.

5

TXB

Transmit buffer interrupt. Indicates that a TxBD was updated.

6

RFINT

Receive frame interrupt. Indicates that a frame was received and that the last corresponding BD

was updated.

7

RXB

Receive buffer interrupt. Indicates that a RxBD was updated.

8

MII

MII interrupt. Indicates that the MII completed the requested data transfer.

9

EBERR Ethernet bus error occurred. Indicates that a bus error occurred when the FEC was accessing the

U bus.

10Р31

С

Reserved. Should written to zero by the host processor.

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

.

..