Table69 . ecntrl field descriptions, Figure69 . i_event/i_mask registers, I_event/i_mask registers -8 – Freescale Semiconductor POWERPC MPC860T User Manual

Page 40: Ecntrl field descriptions -8, Freescale semiconductor, inc

6-8

MPC860T (Rev. D) Fast Ethernet Controller Supplement

MOTOROLA

PRELIMINARYÑSUBJECT TO CHANGE WITHOUT NOTICE

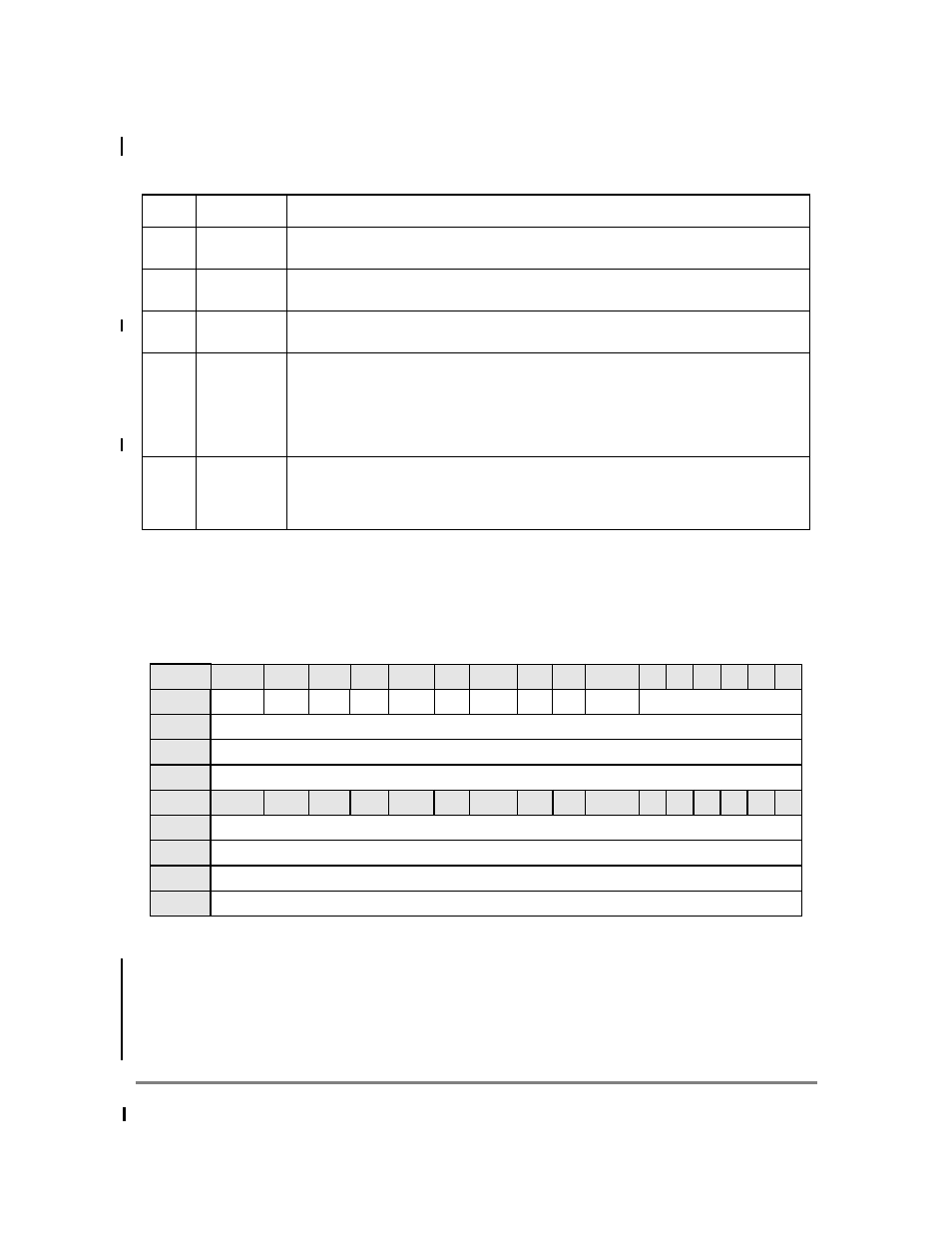

Table 6-9 describes ECNTRL Þelds.

6.2.9 Interrupt Event (I_EVENT)/Interrupt Mask Register (I_MASK)

When an event sets a bit in the interrupt event register (I_EVENT), shown in Figure 6-9, an

interrupt is generated if the corresponding interrupt mask register (I_MASK) bit is set.

I_EVENT bits are cleared by writing ones; writing zeros has no effect.

Table 6-10 describes I_EVENT and I_MASK Þelds. Note that neither the RxBD or TxBD

has an I bit to enable/disable an interrupt on the receive or transmit buffer. As events occur,

they are always reported in I_EVENT, but only those not masked in I_MASK cause an

interrupt. From a system resources and software performance standpoint, it is advisable to

minimize the number of interrupts per frame by masking TXB and RXB in favor of TFINT

Table 6-9. ECNTRL Field Descriptions

Bits

Name

Description

0Р7

С

Reserved. These Þelds may return unpredictable values and should be masked on a read.

Users should always write these Þelds to zero.

8Р28

С

These Þelds may return unpredictable values and should be masked on a read. Users should

always write these Þelds to zero.

29

FEC_PINMUX FEC enable. Read/write. The user must set this bit to enable the FEC function in the 860 in

conjunction with 860 pin multiplexing control.

30

ETHER_EN

Ethernet enable.

0 A transfer is stopped after a bad CRC is appended to any frame being sent.

1 The FEC is enabled, and reception and transmission are possible.

The BDs for an aborted transmit frame are not updated after ETHER_EN is cleared. When

ETHER_EN is cleared, the DMA, BD, and FIFO control logic are reset including BD and FIFO

pointers. See Section 6.3.2, ÒUser Initialization (before Setting ECNTRL[ETHER_EN]).Ó

31

RESET

Ethernet controller reset. When RESET = 1, the equivalent of a hardware or software reset is

performed but it is local to the FEC. ETHER_EN is cleared and all other FEC registers take

their reset values. Also, any transfers are abruptly aborted. Hardware automatically clears

RESET once the hardware reset is complete (approximately 16 clock cycles).

Bits

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Field

HBERR BABR BABT GRA TFINT TXB RFINT RXB

MII

EBERR

Ñ

Reset

0000_0000_0000_0000

R/W

Read/write

Addr

0xE44 (I_EVENT); 0xE48 (I_MASK)

Bits

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Field

Ñ

Reset

0000_0000_0000_0000

R/W

Read/write

Addr

0xE46(I_EVENT); 0xE4A (I_MASK)

Figure 6-9. I_EVENT/I_MASK Registers

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

.

..