Figure61 . addr_low register, Addr_low register -2, Freescale semiconductor, inc – Freescale Semiconductor POWERPC MPC860T User Manual

Page 34

6-2

MPC860T (Rev. D) Fast Ethernet Controller Supplement

MOTOROLA

PRELIMINARYÑSUBJECT TO CHANGE WITHOUT NOTICE

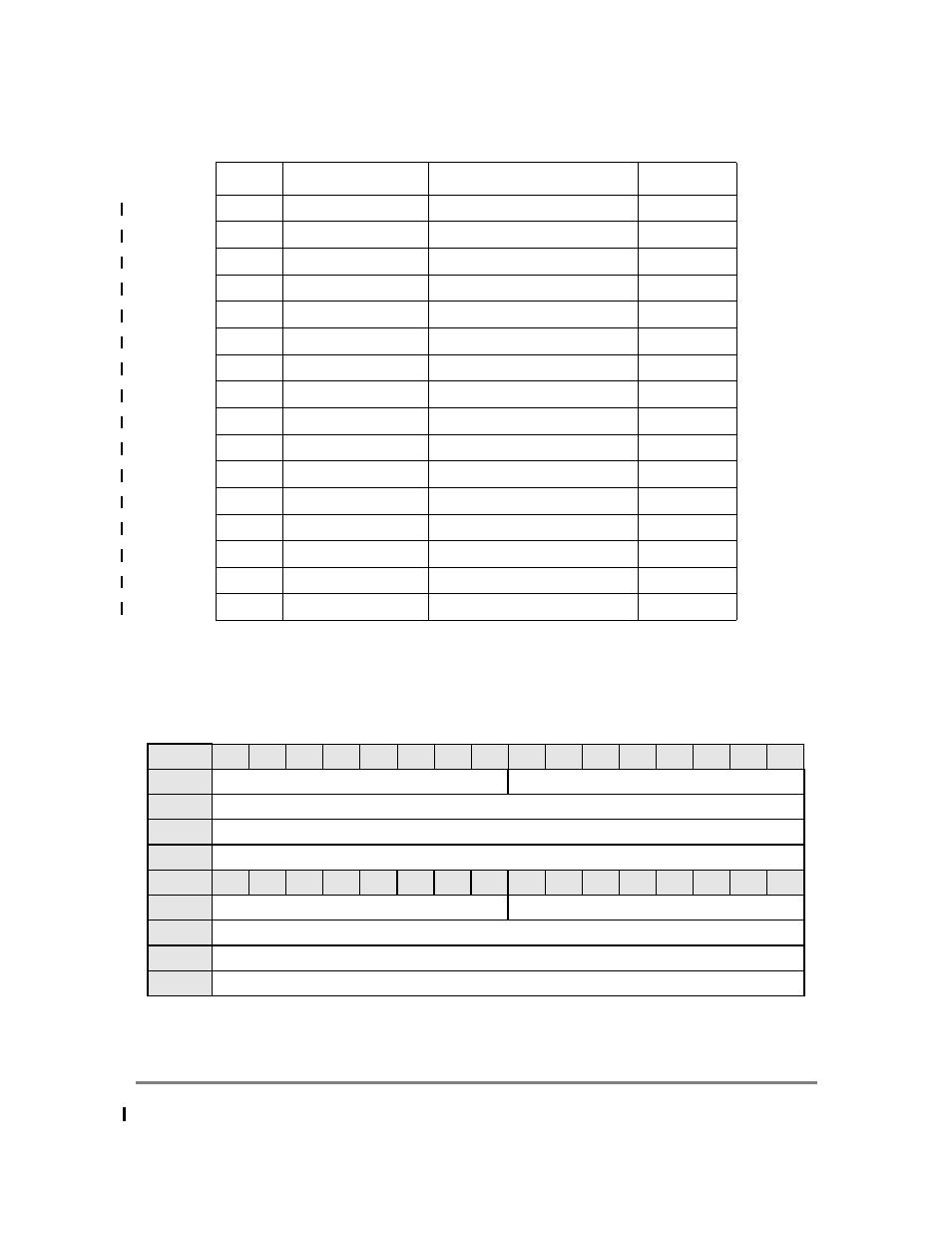

6.2.1 RAM Perfect Match Address Low Register (ADDR_LOW)

The ADDR_LOW register, shown in Figure 6-1, is written by and must be initialized by the

user. It contains the lower 32 bits of the 48-bit address used in the address recognition

process to compare with the destination address Þeld of the receive frames.

0xE40

ECNTRL

Ethernet control register

0xE44

IEVENT

Interrupt event register

0xE48

IMASK

Interrupt mask register

0xE4C

IVEC

Interrupt level and vector status

0xE50

R_DES_ACTIVE

Receive ring updated ßag

0xE54

X_DES_ACTIVE

Transmit ring updated ßag

0xE80

MII_DATA

MII data register

0xE84

MII_SPEED

MII speed register

0xECC

R_BOUND

End of FIFO RAM (read-only)

0xED0

R_FSTART

Receive FIFO start address

0xEE4

X_WMRK

Transmit Watermark

0xEEC

X_FSTART

Transmit FIFO start address

0xF34

FUN_CODE

Function code to SDMA

0xF44

R_CNTRL

Receive control register

0xF48

R_HASH

Receive hash register

0xF84

X_CNTRL

Transmit control register

Bits

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Field

ADDR_LOW BYTE 0

ADDR_LOW BYTE 1

Reset

UndeÞned

R/W

Read/write

Addr

0xE00

Bits

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Field

ADDR_LOW BYTE 2

ADDR_LOW BYTE 3

Reset

UndeÞned

R/W

Read/write

Addr

0xE02

Figure 6-1. ADDR_LOW Register

Table 6-1. FEC Parameter RAM Memory Map (Continued)

Address

Name

Description

Section

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

.

..