Tasw, Tads, Tadh – Mitel DISTRIBUTED HYPERCHANNEL MT90840 User Manual

Page 46: Tddr, Tcsh, Tcss, Tdsw, Tdhw, Tdss, Trws

MT90840

Preliminary Information

2-276

† Timing is over recommended temperature & power supply voltages.

‡ Typical figures are at 25

°

C and are for design aid only: not guaranteed and not subject to production testing.

* High Impedance is measured by pulling to the appropriate rail with R

L

, with timing corrected to cancel time taken to discharge C

L

.

** Individual writes to Connection Memories will have Register Acknowledgment Delay. Burst writes to Connection Memories will have Read

Connection Memory Acknowledgment Delay.

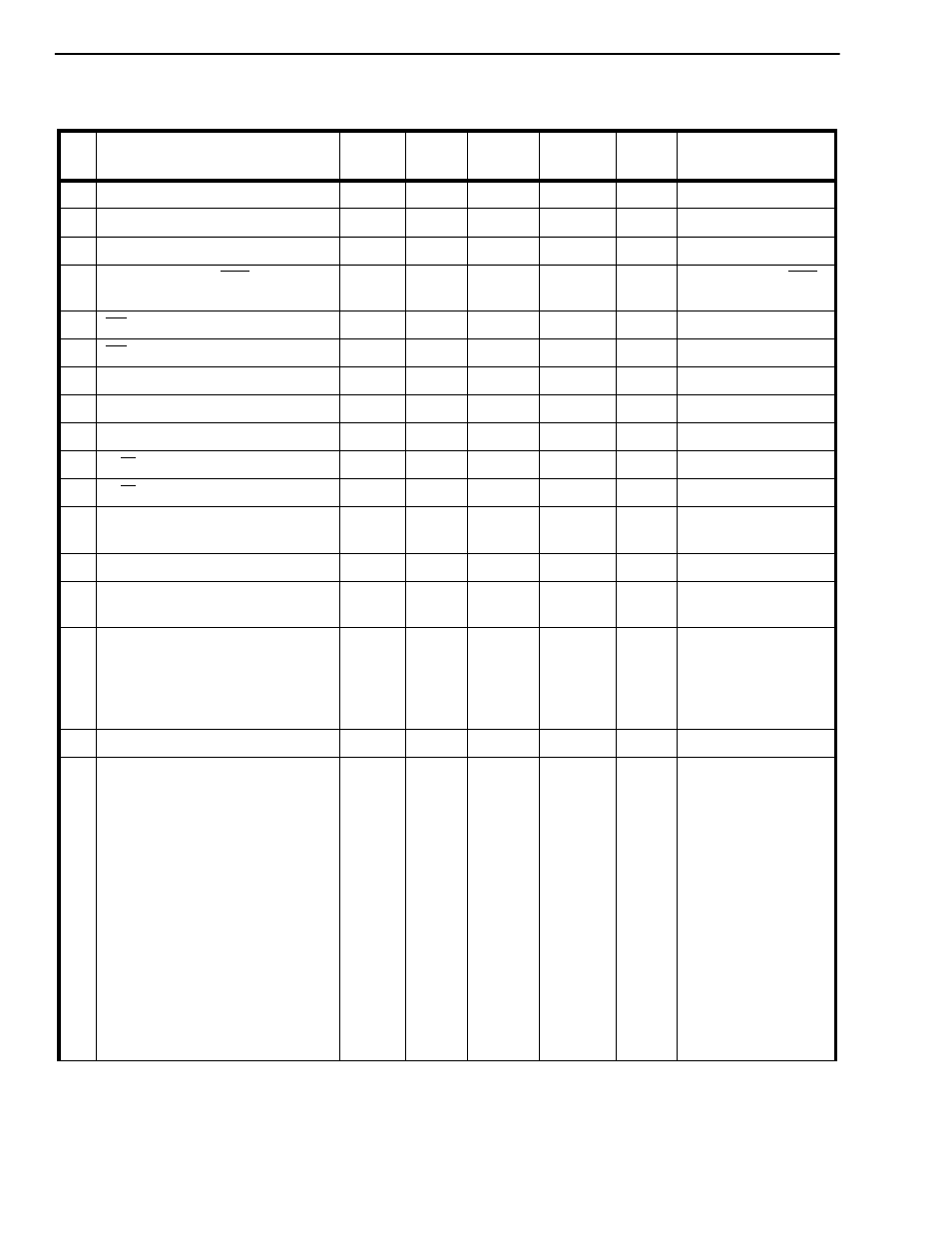

AC Electrical Characteristics

†

- Motorola Multiplexed Bus Mode

Voltages are with respect to ground (V

SS

) unless otherwise stated.

Characteristics

Sym

Min

Typ

‡

Max

Units

Test Conditions/

Notes

1

AS pulse width

t

asw

10

ns

2

Address setup from AS falling

t

ads

5

ns

3

Address hold from AS falling

t

adh

5

ns

4

Data setup from DTA LOW on

read

t

ddr

0

ns

C

L

=150 pF on DTA,

30 pF on AD0-7.

5

CS hold after DS falling

t

csh

0

ns

6

CS setup from DS rising

t

css

0

ns

7

Data setup on write

t

dsw

10

8

Data hold after write

t

dhw

0

ns

9

DS Inactive to AS Falling Edge

t

dss

23

ns

10

R/W setup from DS rising

t

rws

5

ns

11

R/W hold after DS falling

t

rwh

5

ns

12

Data hold after read

t

dhr

10

15

22

30

ns

ns

C

L

=30 pF

C

L

=150 pF

13

DS delay after AS falling

t

dsh

15

ns

14

Acknowledgment hold time

t

akh

0

20

ns

C

L

=150 pF,

R

L

=1k

Ω∗

15

Acknowledgment Delay:

Writing Registers

Acknowledgment Delay:

Reading Registers

t

akd-wr

t

akd-rd

32

41

73

85

ns

ns

ns

ns

C

L

=30 pF

C

L

=150 pF

C

L

=30 pF

C

L

=150 pF

16

Memory Acknowledgment Delay

t

akd-mem

Reading TP Data Memory

Reading RP Data Memory

Reading TP Connection

Memory

Reading RP Connection

Memory

Writing TP Connection

Memory**

Writing RP Connection

Memory**

244

122

1

clock

cycle

244

t

akd-wr

t

akd-wr

488

366

2 clock

cycles

488

1306

1062

3 clk

cyc +

t

akd-rd

817

3 clk

cyc +

t

akd-wr

774

ns

ns

ns

ns

1 to 5 C4 cycles +

register t

akd-rd

.5 to 4 C4 cycles +

register t

akd-rd

1 to 3 PCKT/R

cycles + register

t

akd-rd

1 to 3 C4 cycles +

register t

akd-rd

Up to 3 PCKT/R

cyc. + register t

akd-wr

Up to 3 C4 cycles +

register t

akd-wr