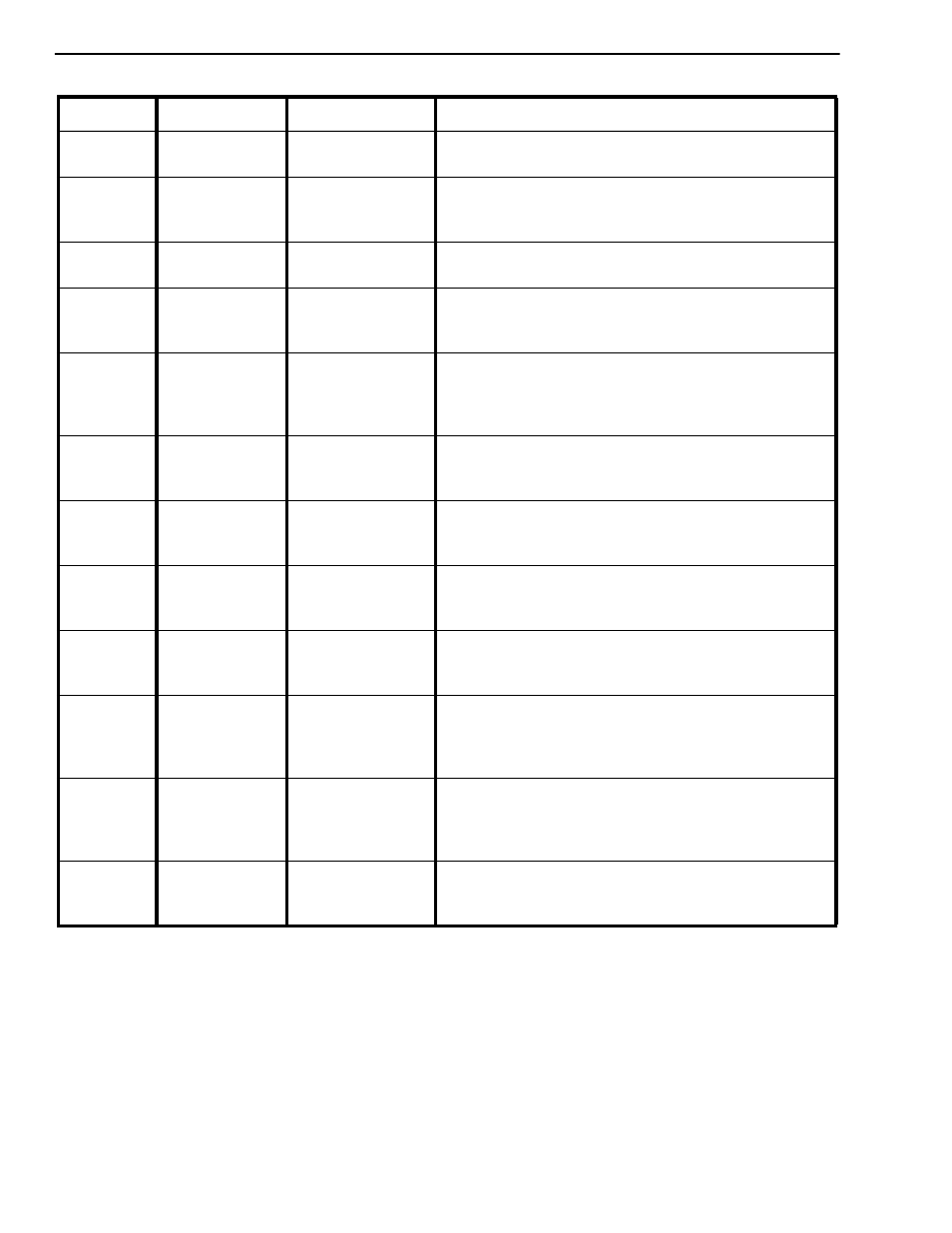

Table 1 - mt90840 throughput delay summary, Preliminary information – Mitel DISTRIBUTED HYPERCHANNEL MT90840 User Manual

Page 16

MT90840

Preliminary Information

2-246

Table 1 - MT90840 Throughput Delay Summary

Naming rules:

ELD: ELastic Delay, measured from PPFRi to F0i (4.4 to 129.4

µ

sec).

P/S:Parallel-to-Serial data path.

Pi:Parallel Input channel time, expressed in delay after PPFRi (0 to 125

µ

sec).

Po:Parallel Output channel time, expressed in delay after PPFTi/o (0 to 125

µ

sec).

S/P:Serial-to-Parallel data path.

Si:Serial Input channel time, expressed in delay after F0i/o (0 to 125

µ

sec).

So: Serial Output channel time, expressed in delay after F0i/o (0 to 125

µ

sec).

Transmission:The delay due to electronic circuits and physical media connecting the parallel ports of two MT90840s. (Assumed to be

negligible in TM3.)

Note 1: Exact P/S or S/P delay depends on relative positions of PPFRi and F0 +/- 120 nsec tolerance).

Note 2: Actual TM1 P/S and P/P delay depends on elastic position of PPFRi with respect to F0i (see ELD definition).

Note 3: Bypass delay in TM2: PPFT and PDo ch.0 are co-incident with PDi ch.235 at 19.44 MHz, ch.199 at 16 MHz, and ch.80 at 6.48

MHz. (TCP = 1 delays PDo ch.0 an extra half clock-cycle in TM2).

Note 4: “Round-trip” delay from/to serial ports with the same F0 is always an integral number of frames (plus switching: So - Si).

Mode

Data Rates

Minimum Delay

Total Throughput Delay

TM1, TM2,

or TM3 S/P

All

Dmin = 7.7

µ

sec

Note 1

D = Dmin + 1 frame + Po - Si = 132.7

µ

sec + Po - Si

Min. 7.7

µ

sec, Avg. 133

µ

sec, Max. 258

µ

sec

TM1P/S

All

Dmin = ELDmin

= 4.4

µ

sec

Note 2

D = 1 frame + ELD + So - Pi = 125

µ

sec + ELD + So - Pi

Min. 4.4

µ

sec, Max. 379

µ

sec

TM2 P/S

All

Dmin = 4.3

µ

sec

Note 1

D = Dmin + 1 frame + So - Pi = 129.3

µ

sec + So - Pi

Min. 4.3

µ

sec, Avg. 129

µ

sec, Max. 254

µ

sec

TM3 P/S

All

Dmin = 1 frame -

7.7

µ

sec

= 117.3

µ

sec

T = Dmin + 1 frame + So - Pi = 242.3

µ

sec + So - Pi

Min. 117

µ

sec, Avg. 242

µ

sec, Max. 367

µ

sec

TM1 P/P

(Bypass)

All

Dmin = 12

µ

sec +

1 frame

= 137

µ

sec

Note 2

D = 7.7

µ

sec + 1 frame + ELD

Min.137

µ

sec, Max. 262

µ

sec

TM2 P/P

(Bypass)

19.44 Mbyte/s

16.384 Mbyte/s

6.480 Mbyte/s

Note 3

D = {235 or 235.5} PCKR cycles = 12

µ

sec

D = {199 or 199.5} PCKR cycles = 12

µ

sec

D = {80 or 80.5} PCKR cycles = 12

µ

sec

TM4 P/P

(Switching)

19.44 & 16.384

Mbyte/s

Dmin = {3.5 or 4}

PCKR cycles

(TCP bit = 1 or 0)

D = Dmin + 1 frame + Po - Pi

Min. < 0.3

µ

sec, Avg. 125

µ

sec, Max. 250

µ

sec

TM1 S/P +

TM2 P/S

All

Dmin = 12

µ

sec +

1 frame

= 137

µ

sec

D = 12

µ

s + 2 frames + Transmission + So - Si

= 262

µ

sec + Transmission + So - Si

TM2 S/P +

TM1 P/S

All

Dmin = 12

µ

sec +

1 frame

= 137.4

µ

sec

D = 12

µ

sec + 2 frames + Transmission + ELD + So - Si

= 262

µ

sec + Transmission + ELD + So - Si

TM1 S/P +

TM2 P/S +

TM2 S/P +

TM1 P/S

All

Dmin = 4 frames

= 500

µ

sec

D = (2 X 12)

µ

sec + 4 frames + 2 X Transmission + ELD

+ So - Si = {5 or more integral frames} + So - Si

(Note 4)

TM1 S/P +

TM2

Bypass +

TM1 P/S

All

Dmin = 2 frames

= 250

µ

sec

D = (3 X 12)

µ

sec + 2 frames + 2 X Transmission + ELD

+ So - Si

= {3 or more integral frames} + So - Si

(Note 4)

TM3 S/P +

TM3 P/S

All

Dmin = 250

µ

sec

D = (7.7 + 117.3)

µ

sec + 2 frames + So - Si

= 375

µ

sec + So - Si

Min. 250

µ

sec, Avg. 375

µ

sec, Max. 500

µ

sec (Note 4)