Figure 25 - timing for the parallel port external, Figure 26 - tm1 parallel port transmit timing (tm1, Preliminary information – Mitel DISTRIBUTED HYPERCHANNEL MT90840 User Manual

Page 41

Preliminary Information

MT90840

2-271

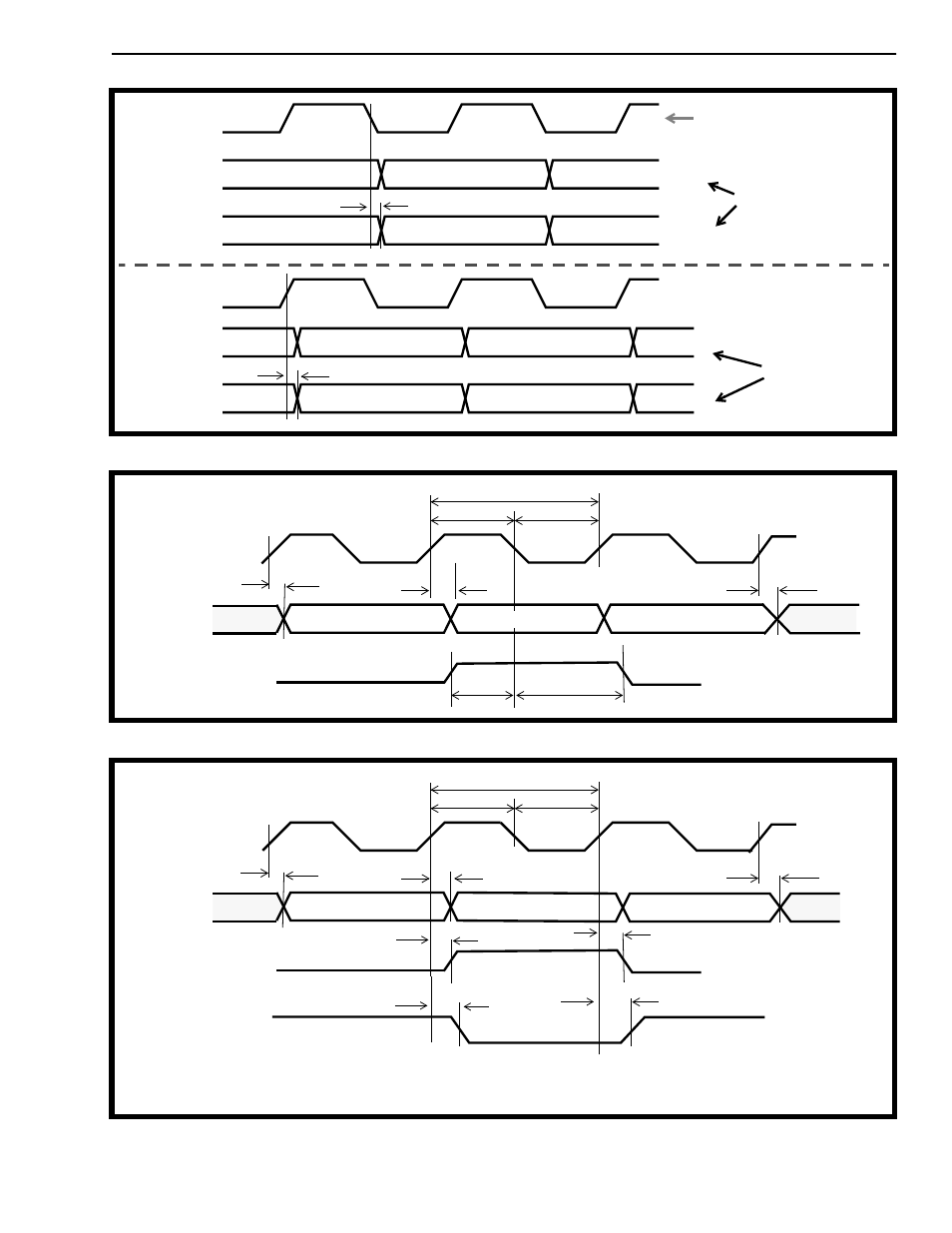

Figure 25 - Timing for the Parallel Port External Control Lines CTo0-3

Figure 26 - TM1 Parallel Port Transmit Timing (TM1 & PFDI = 1, PPFT is an input)

Figure 27 - Parallel Port Transmit Timing (PFDI = 0, PPFT is an output)

PDo0-7

CTo0-3

PCKT/PCKR

TCP controls the clock-edge

on which the output changes.

byte m-1

byte m

byte m+1

TCP = 1

PDo0-7

CTo0-3

byte m-1

byte m

byte m+1

CTo corresponding to

byte m

CTo corresponding to

byte m+1

PCKT/PCKR

t

cdf

TCP = 0

t

cdf

CTo corresponding to

byte m

CTo corresponding to

byte m+1

byte 0

t

sod

PDo0-7

byte 1

t

PPFH

PCKT

PPFTi (PPFP=1)

t

az

t

clkh

t

clk

t

clkl

t

za

t

PPFS

tristate

tristate

byte n

n = 2429, 2047, or 809

byte 0

t

sod

PDo0-7

byte n

byte 1

t

df

t

df

PCKT/PCKR

PPFTo (PPFP=1)

t

df

t

df

Note: The depicted output timing occurs when TCP = 0. If TCP = 1, the byte at PDo0-7 port and the PPFT line will be

output on the falling edge of the PCKT/PCKR clock.

t

az

t

za

t

clkh

t

clk

t

clkl

tristate

tristate

PPFTo (PPFP=0)