Mitel DISTRIBUTED HYPERCHANNEL MT90840 User Manual

Distributed hyperchannel switch, Preliminary information, Features

2-231

Features

•

Time slot interchange function between eight

pairs of ST-BUS/GCI/MVIP

streams (512

channels) and parallel data port

•

Programmable data rates on the parallel port

(19.44, 16.384, or 6.480 Mbyte/s)

•

Programmable data rates on the serial port

(2.048 Mbps, 4.096 Mbps or 8.192 Mbps)

•

Supports star and point-to-point connections, and

unidirectional or bidirectional ring topologies for

distributed systems

•

Input-to-output bypass function on the parallel

data port for use in add/drop applications

•

Provides elastic buffer at parallel input port in the

receive direction

•

Provides byte switching for up to 2430 channels

•

Per-channel direction control on the serial port

side

•

Per-channel message mode and high-impedance

control on both parallel and serial port sides

•

8-bit multiplexed microprocessor port compatible

with Intel and Motorola microcontrollers

•

Guarantees frame integrity when switching nX64

wideband channels such as ISDN H0 channel

•

Provides external control lines allowing fast

parallel interface to be shared with other devices

•

Diagnostic alarm functions and clock

phase-status word for clock monitoring

•

IEEE 1149 (JTAG) boundary scan port

Applications

•

Bridging ST-BUS/MVIP buses to high speed

Time Division Multiplexed backplanes at

SONET rates (STS-1, STS-3)

•

High speed isochronous backbones for

distributed PBX and LAN systems

•

Switch platforms of up to 2430 channels with

guaranteed frame integrity for wideband

channels

•

Serial bus control and monitoring

•

Data multiplexing

•

High speed communications interface

ISSUE 2

March 1997

Ordering Information

MT90840AL

100 Pin PQFP

MT90840AP

84 Pin PLCC

-40

°

C to 85

°

C

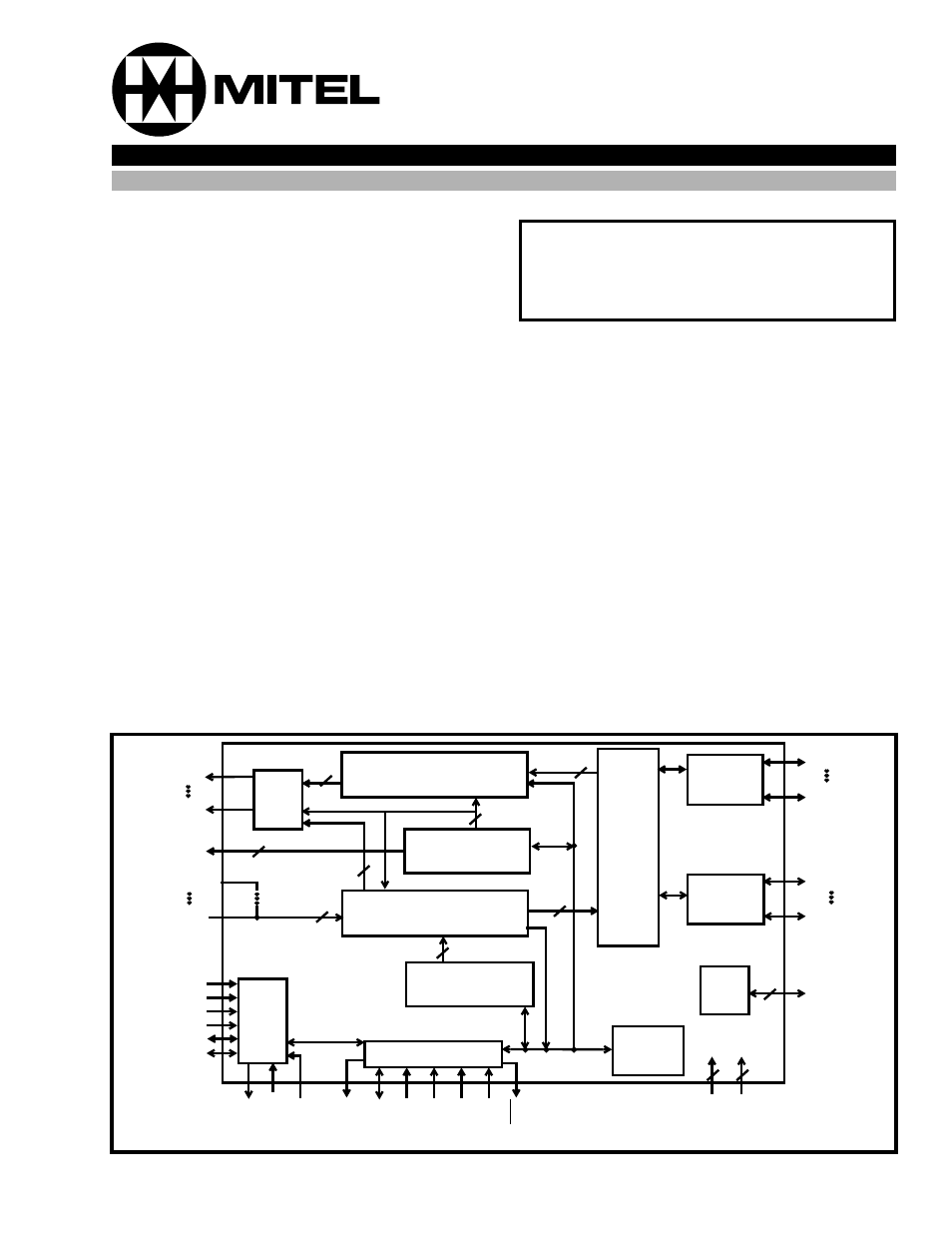

Figure 1 - Functional Block Diagram

MT90840

Distributed Hyperchannel Switch

Output

Mux &

PDo0

PDo7

2430 Position

TX Path

Connection Memory

Bidirectional

I/O

Driver

8

Serial

to

Parallel

&

Parallel

to

Serial

Conver-

Bidirectional

I/O

Driver

STi7

STi0

STo7

STo0

4

CTo0-3

Timing

Control

Unit

PDi0

PDi7

PCKR

PCKT

RES

PPFRi

PPFTi/o

F0i/o

CPU Interface

Internal

Registers

TEST

Pins

5

8

8

SPCKo

C4/8R1

C4/8R2

IRQ

AD0-7

R/W\WR

AS/ALE

CS

DTA

VDD

VSS

DS/RD

ters

Multiple Pages of 512 Position

TX Path Data Memory

8

512 Position

RX Path

8

Multiple Pages of 2430-Byte

RX Path Data Memory

15

8

8

Connection Memory

JTAG

Drivers

16

Preliminary Information

Document Outline

- ISSUE 2 March 1997

- Figure 1 - Functional Block Diagram

- MT90840 DistributedHyperchannelSwitch

- Figure 2 - Pin Connections

- 3

- 43

- DS/RD

- 4

- 44

- AS/ALE

- 5

- 45

- CS

- 6

- 46

- DTA

- 7

- 47

- IRQ

- 8

- 48

- RES

- 9

- 49

- IC

- 10, 26,

- 27

- 1-4, 27-31

- 50-54

- 76-80

- NC

- 13-20

- 57-64

- STi0-STi7

- 21

- 65

- C4/8R1

- 22

- 66

- F0i/o

- 23

- 67

- C4/8R2

- 28-31

- 70-73

- CTo3-

- CTo0

- 34-41

- 81-88

- PDo7-PDo 0

- 42

- 89

- PPFTi/o

- 45-52

- 92-99

- PDi7-0

- 55

- 6

- PCKR

- 56

- 7

- PCKT

- 57

- 8

- PPFRi

- 58

- 9

- TDI

- 59

- 10

- TRST

- 60

- 11

- TCK

- 61

- 12

- TMS

- 62

- 13

- TDO

- 65

- 16

- SPCKo

- 66-73

- 17-24

- STo7-STo0

- 76-83

- 32-39

- AD0-AD7

- 84

- 40

- R/W \ WR

- 1,11 24,32, 43,53, 64,74

- 15,25, 41,55, 68,74, 90,10 0

- VSS

- 2, 12, 25,33 44,54, 63,75

- 5, 14, 26,42 56,69, 75,91

- VDD

- Transmit Path Connection Memory

- Transmit Path Data Memory

- Receive Path Connection Memory

- Receive Path Data Memory

- Bypass

- Parallel Switching

- 2.048 Mbps Balanced Mode

- 2.048 Mbps Add/Drop Mode

- 4.096 Mbps Mode

- 8.192 Mbps Mode

- Serial Port Clock Signals

- Internal 4.096 MHz Clock Generator

- Serial Frame Pulse

- Parallel Port Clock Signals and Framing

- Asynchronous Parallel Port With ST-BUS Clock Maste...

- TM1 Multiple-MT90840 Sub-Mode (PFDI)

- Asynchronous Parallel Port With ST-BUS Clock Slave...

- Internal 4.096 MHz Clock Divider

- External PLL and C4 Phase-Correction

- TM2 Multiple-MT90840 Sub-Mode (SFDI)

- Synchronous Parallel Port With ST-BUS Clock Slave

- Per-channel Bypass on the Parallel Port

- Per-channel Control Outputs on the Parallel Port

- Per-channel Tri-state (Serial and Parallel)

- Per-channel Message Mode (Serial and Parallel)

- Per-channel Direction Control on the Serial Port

- 2.048 Mbps Balanced Mode

- Figure 11a - 2.048 Mbps Balanced Mode TPDM Address...

- Figure 11b - 2.048 Mbps Balanced Mode RPCM Address...

- Figure 12a - 2.048 Mbps Add/Drop Mode TPDM Address...

- Figure 12b - 2.048 Mbps Add/Drop Mode RPCM Address...

- Figure 13a - 4.096 Mbps TPDM Addressing

- Figure 13b - 4.096 Mbps RPCM Addressing

- Figure 14a - 8.192 Mbps TPDM Addressing

- Figure 14b - 8.196 Mbps RPCM Addressing

- Figure 15 - A Typical Boundary-Scan IC

- Table 4 - Boundary-Scan Register

- Table 4 - Boundary Scan Register

- Figure 3 - Serial Port Interface Functional Timing...

- Figure 6b - TM2 Multiple-MT90840 Configuration

- Table 1 - MT90840 Throughput Delay Summary

- Figure 9 - Parallel Port Control Outputs, CTo0-3

- Figure 10 - Balanced Per-Channel Serial Direction ...

- 0

- 0

- 0

- 0

- 0

- 0

- R/W

- IMS Register

- 60

- 0

- 0

- 0

- 0

- 1

- 1

- R/W

- Control Register

- 00

- 0

- 0

- 0

- 1

- 0

- 2

- R/W

- TIM Register

- 00

- 0

- 0

- 0

- 1

- 1

- 3

- R/W

- GPM Register

- 00

- 0

- 0

- 1

- 0

- 0

- 4

- R/W

- ALS Register

- 0X

- 0

- 0

- 1

- 0

- 1

- 5

- R/W

- Test (leave 00hx)

- 00

- 0

- 0

- 1

- 1

- 0

- 6

- -

- reserved

- 0

- 0

- 1

- 1

- 1

- 7

- -

- reserved

- 0

- 1

- 0

- 0

- 0

- 8

- RO

- Phase Status (Low byte)

- XX

- 0

- 1

- 0

- 0

- 1

- 9

- RO

- Phase Status (High 3 bits)

- 0X

- 0

- 1

- 0

- 1

- 0

- 10

- -

- reserved

- DR1-0 Serial Port Data Rate Selection. Select one ...

- DR1 DR0 Data Rate

- 0 0 2.048 Mbps

- 0 1 4.096 Mbps

- 1 0 8.192 Mbps

- 1 1 reserved

- PPS1-0 Parallel Port Data Rate Selection. Select o...

- PPS1 PPS0 Data Rate

- 0 0 reserved. Do not use.

- 0 1 6.480 Mbyte/s.

- 1 0 19.44 Mbyte/s.

- 1 1 16.384 Mbyte/s.

- ODE Output Drive Enable. When LOW, forces the MT90...

- FDC Full Direction Control. This bit should only b...

- Note: Bits 1 & 2 must be set to 0 by the CPU.

- TM1-0 Timing Mode control bits. Define the four di...

- 0 0 Timing Mode 1

- 0 1 Timing Mode 2

- 1 0 Timing Mode 3

- 1 1 Timing Mode 4

- C4/8R C4/8R Input Reference Select. If set high, t...

- TCP Parallel Port Transmit Clock Polarity. To allo...

- INTCLK Internal 4.096 MHz Clock Divider. For use i...

- SFDI Serial Frame Pulse Direction Control. Normall...

- PFDI Parallel Frame Pulse Direction Control. Norma...

- Note: Bit 7 must be set to 0 by the CPU.

- BPD7-4 Block-Programming Data bits 7-4. These bits...

- PPFP Parallel Port Frame pulse Polarity. Used to p...

- DIN Device Initialization. This bit is used in TM1...

- SPFP Serial Port Framing Polarity. In TM2 and TM3 ...

- BPE Block-Programming Enable. This bit activates t...

- Note: The CPU must maintain the required settings ...

- MSK3-0 Mask Alarm Bits 3-0. These bits mask the sp...

- PPCE Parallel Port Frame Counter Error. Used in al...

- RXPAA RX Phase Alignment Alarm. Used in TM2 operat...

- TXPAA TX Phase Alignment Alarm. Used in TM1 operat...

- FSA Frame Slip on Elastic Buffer. Used in TM1 oper...

- Note: The interrupt source bits are latched, and r...

- This register selects which 128 byte page of which...

- SEL2-0 Memory Select bits. Used by the CPU to sele...

- SEL2 SEL1 SEL0 Memory Selected for RD/WR operation...

- 0 0 0 Receive Path Connection Memory Low (RPCM Low...

- 0 0 1 Receive Path Connection Memory High (RPCM Hi...

- 0 1 0 Receive Path Data Memory (RPDM)

- 0 1 1 Enable Memory Block-Programming feature for ...

- 1 0 0 Transmit Path Connection Memory Low (TPCM Lo...

- 1 0 1 Transmit Path Connection Memory High (TPCM H...

- 1 1 0 Transmit Path Data Memory (TPDM)

- 1 1 1 Enable Memory Block-Programming feature for ...

- HA11-7 High Address Bits 11-7. These bits select w...

- To address serial time slots in TPDM or RPCM:

- To address parallel time slots in RPDM or TPCM:

- PSD10-0 Phase Status Data 10-0. The PSD bits repre...

- OE/CTo0 Output Enable. Provides per channel trista...

- PPBY Parallel Port Bypass Enable. Indicates that t...

- MC Message Channel. The message channel contents a...

- CTo1-3 External Control Lines 1-3. These three bit...

- AB8-11 Source Channel Address Bits 8-11. These bit...

- AB7-0 Source Channel Address Bits. In Timing Modes...

- In Timing Mode 4, these 8 bits are used along with...

- If message mode is selected at TPCM High bits, the...

- MC Message Channel: The message channel contents a...

- DC Direction Control: DC set HIGH indicates this c...

- When FDC = LOW (2.048, 4.096 or 8.192 Mbps) the 51...

- When FDC = HIGH (2.048 Mbps), the 512 DC bits can ...

- OE Output Enable. Per-channel tristate control for...

- AB8-11 Source Channel Address. These 4 bits are us...

- AB0-7 Source Channel Address. In switching mode (M...

- Figure 16 - CTI Distributed Architecture Implement...

- 1

- VDD

- 0

- 6

- V

- 2

- VI

- VSS-0.3

- VDD+0.3

- V

- 3

- IO

- 40

- mA

- 4

- TS

- -65

- +150

- °C

- 5

- PD

- 2

- W

- 1

- TOP

- -40

- +85

- °C

- 2

- VDD

- 4.75

- 5.0

- 5.25

- V

- 3

- VI

- 0

- VDD

- V

- 1

- I

- N

- P

- U

- T

- S

- IDD

- 100

- 160

- mA

- 2

- VIH

- 2.0

- V

- 3

- VIL

- 0.8

- V

- 4

- VT+

- 2.8

- 4.2

- V

- 5

- VT-

- 0.9

- 1.8

- V

- 6

- IIL

- 50

- mA

- 7

- CI

- 10

- pF

- 8

- O

- U

- T

- P

- U

- T

- S

- VOH

- 2.4

- V

- 9

- VOL

- 0.4

- V

- 10

- IOH

- or

- IOL

- 9

- mA

- 16

- mA

- 28

- mA

- 11

- IOZ

- 5

- mA

- 12

- CO

- 10

- pF

- 1

- tclk

- 200

- 100

- 224

- 241

- 244

- 122

- 259

- 245

- ns

- ns

- ns

- ns

- 2

- tclkh

- 85

- 50

- 101

- 110

- 122

- 61

- 135

- ns

- ns

- ns

- ns

- 3

- tclkl

- 85

- 50

- 101

- 110

- 122

- 61

- 135

- ns

- ns

- ns

- ns

- 4

- tt

- 5

- ns

- 5

- 6

- tfrs

- 0

- 28

- ns

- ns

- 7

- tfrh

- 8

- 0

- ns

- ns

- 8

- tfrw

- 35

- ns

- 9

- taz

- 38

- 50

- 26

- ns

- ns

- ns

- 10

- tza

- 38

- 50

- 26

- ns

- ns

- ns

- 11

- tsod

- 40

- 64

- 52

- 72

- 28

- 43

- ns

- ns

- ns

- ns

- ns

- ns

- 12

- tstis

- 28

- 41

- 0

- 0

- ns

- ns

- ns

- 13

- tstih

- 9

- 2

- 20

- 13

- ns

- ns

- ns

- Figure 17 - Output Test Load

- Figure 18 - Serial Port Timing for 2.048 Mbps Oper...

- Figure 19 - Serial Port Timing for 2.048 Mbps - TM...

- Figure 20 - Serial Port Timing for 4.096 Mbps Oper...

- Figure 21 - Serial Port Timing for 4.096 Mbps Oper...

- Figure 22 - Serial Port Timing for 8.192 Mbps - TM...

- Figure 23 - Per-Channel Tristate Characteristics a...

- Figure 24 - Serial Port Timing for 8.192 Mbps - Ti...

- Figure 25 - Timing for the Parallel Port External ...

- Figure 26 - TM1 Parallel Port Transmit Timing (TM1...

- Figure 28 - Parallel Port Receive Timing

- 1

- tclk

- 50

- ns

- 2

- 20

- ns

- 3

- 20

- ns

- 4

- 28

- 30

- ns

- 5

- 28

- 30

- ns

- 6

- 26

- 28

- ns

- 7

- 26

- ns

- 8

- 28

- ns

- 9

- 5

- ns

- 10

- 8

- ns

- 11

- 5

- ns

- 12

- 8

- ns

- 13

- 5

- ns

- 14

- 5

- ns

- 15

- -100

- +100

- ns

- 1

- talw

- 10

- ns

- 2

- tads

- 5

- ns

- 3

- tadh

- 5

- ns

- 4

- talrd

- 15

- ns

- 5

- tddr

- 0

- ns

- 6

- tcsrw

- 0

- ns

- 7

- tcsr

- 0

- ns

- 8

- tdhr

- 10

- 15

- 22

- 30

- ns

- ns

- 9

- talwr

- 15

- ns

- 10

- tcsw

- 0

- ns

- 11

- tdsw

- 10

- ns

- 12

- tdhw

- 0

- ns

- 13

- trst

- 23

- ns

- 14

- takh

- 0

- 20

- ns

- 15

- trdd

- 47

- 68

- ns

- ns

- 16

- takd-rd

- takd-wr

- 73

- 85

- 32

- 41

- ns

- ns

- ns

- ns

- 17

- takd-mem

- 244

- 122

- 1 clock cycle

- 244

- takd-wr

- takd-wr

- 488

- 366

- 2 clock cycles

- 488

- 1306

- 1062

- 3 clk cyc + takd-rd

- 817

- 3 clk cyc + takd-wr

- 774

- ns

- ns

- ns

- ns

- 1

- tasw

- 10

- ns

- 2

- tads

- 5

- ns

- 3

- tadh

- 5

- ns

- 4

- tddr

- 0

- ns

- 5

- tcsh

- 0

- ns

- 6

- tcss

- 0

- ns

- 7

- tdsw

- 10

- 8

- tdhw

- 0

- ns

- 9

- tdss

- 23

- ns

- 10

- trws

- 5

- ns

- 11

- trwh

- 5

- ns

- 12

- tdhr

- 10

- 15

- 22

- 30

- ns

- ns

- 13

- tdsh

- 15

- ns

- 14

- takh

- 0

- 20

- ns

- 15

- takd-wr

- takd-rd

- 32

- 41

- 73

- 85

- ns

- ns

- ns

- ns

- 16

- takd-mem

- 244

- 122

- 1 clock cycle

- 244

- takd-wr

- takd-wr

- 488

- 366

- 2 clock cycles

- 488

- 1306

- 1062

- 3 clk cyc + takd-rd

- 817

- 3 clk cyc + takd-wr

- 774

- ns

- ns

- ns

- ns

- A

- 0.165

- (4.20)

- 0.200

- (5.08)

- A1

- 0.090

- (2.29)

- 0.130

- (3.30)

- D/E

- 0.185

- (30.10)

- 1.195

- (30.35)

- D1/E1

- 1.150

- (29.210)

- 1.158

- (29.413)

- D2/E2

- 1.090

- (27.69)

- 1.130

- (28.70)

- F

- 0.026

- (0.661)

- 0.032

- (0.812)

- G

- 0.013

- (0.331)

- 0.021

- (0.533)

- H

- 0.050 BSC

- (1.27 BSC)

- I

- 0.020

- (0.51)

- A1

- 0.002

- (0.05)

- 0.02

- (0.5)

- A2

- 0.101

- (2.57)

- 0.113

- (2.87)

- b

- 0.008

- (0.20)

- 0.016

- (0.40)

- c

- 0.004

- (0.10)

- 0.008

- (0.20)

- D

- 0.547

- (13.9)

- 0.555

- (14.1)

- E

- 0.783

- (19.9)

- 0.791

- (20.1)

- e

- 0.26 nominal

- (0.65) nominal

- Hd

- 0.695

- (17.65)

- 0.715

- (18.15)

- He

- 0.931

- (23.65)

- 0.951

- (24.15)

- L

- 0.025

- (10.65)

- 0.037

- (0.95)

- L1

- 0.077 nominal

- (1.95) nominal

- Y

- 0.004

- (0.10)

- q

- 0

- (0)

- 10

- (10)