Zeus address map – Eurotech Appliances ZEUS PXA270 User Manual

Page 19

ZEUS Technical Manual

Detailed hardware description

© 2007 Eurotech Ltd Issue D

19

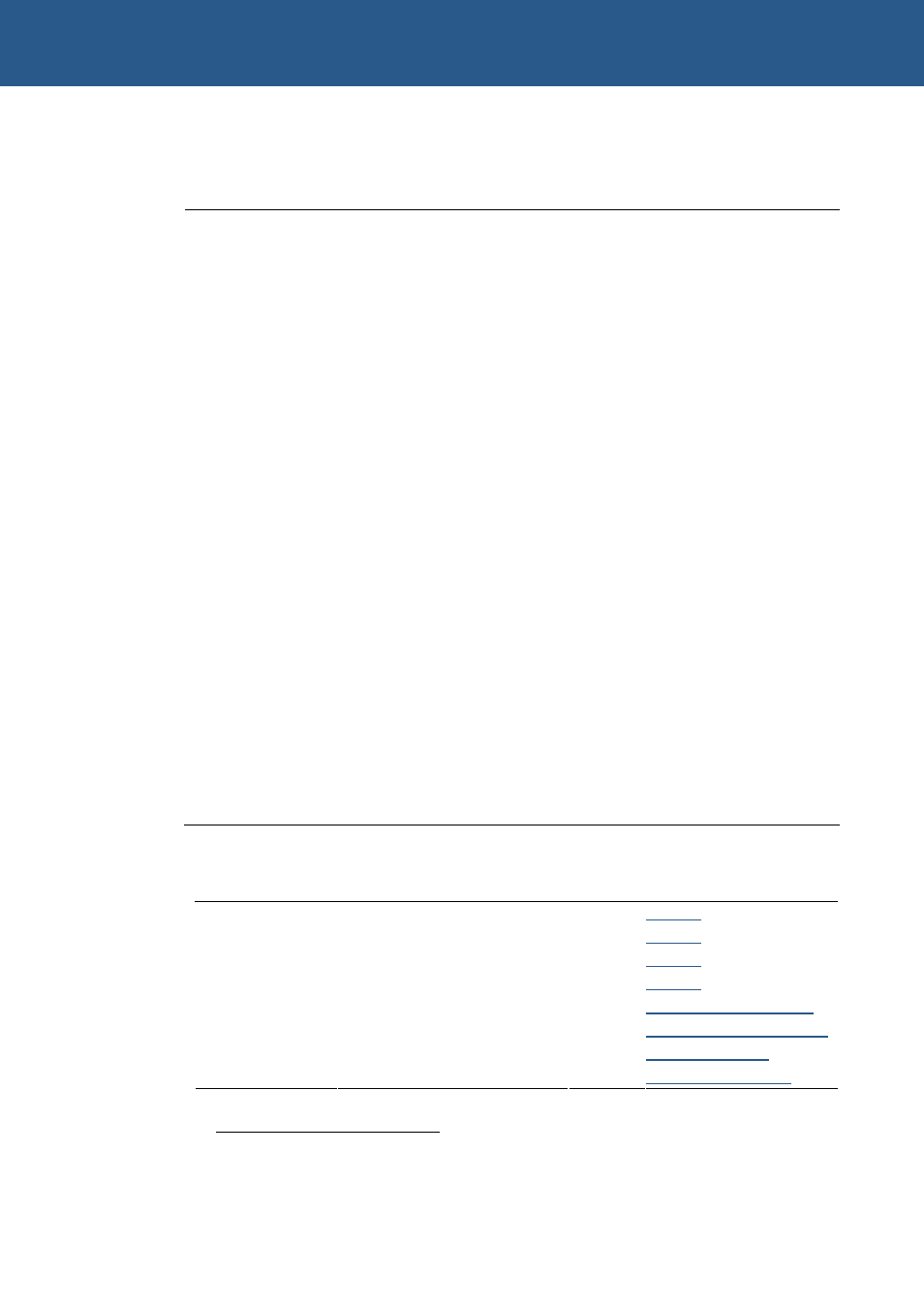

ZEUS address map

PXA270 chip select Physical address Bus

width

Description

CS0#

0x00000000 – 0x03FFFFFE

16-bit

Flash memory/Silicon disk

CS1#

0x04000000 – 0x07FFFFFE

16-bit

Ethernet controller 0

CS2# 0x08000000

–

0x0BFFFFFE

16-bit

Ethernet controller 1

CS3# 0x0C000000

–

0x0FFFFFFF

-

Reserved

CS4#

0x10000000 – 0x11FFFFFE

16-bit

Quad UART

0x12000000 – 0x13FFFFFE

16-bit

CPLD registers

CS5# 0x14000000

–

0x17FFFFFE

16-bit

SRAM

- 0x18000000

–

0x1FFFFFFF

-

Reserved

- 0x20000000

–

0x2FFFFFFE

16-bit

CompactFlash

-

0x30000000 – 0x300003FF

8/16-bit

PC/104 I/O space

- 0x30000400

–

0x3BFFFFFF

-

Reserved

-

0x3C000000 – 0x3C1FFFFF

8/16-bit

PC/104 memory space

- 0x3C200000

–

0x3FFFFFFF

-

Reserved

-

0x40000000 – 0x43FFFFFF

32-bit

PXA270 peripherals

- 0x44000000

–

0x47FFFFFC

32-bit

LCD control registers

1

- 0x48000000

–

0x4BFFFFFC

32-bit

Memory controller registers

1

-

0x4C000000 – 0x4FFFFFFC

32-bit

USB host registers

1

- 0x50000000

–

0x53FFFFFC

32-bit

Capture interface registers

1

- 0x54000000

–

0x57FFFFFC

32-bit

Reserved

-

0x58000000 – 0x5BFFFFFC

32-bit

Internal memory control

1

-

0x5C000000 – 0x5C00FFFC

32-bit

Internal SRAM bank 0

-

0x5C010000 – 0x5C01FFFC

32-bit

Internal SRAM bank 1

-

0x5C020000 – 0x5C02FFFC

32-bit

Internal SRAM bank 2

-

0x5C030000 – 0x5C03FFFC

32-bit

Internal SRAM bank 3

- 0x5C040000

–

0X7FFFFFFF

-

Reserved

SDCS0#

0x80000000 – 0x8FFFFFFF

32-bit

SDRAM (U2/U3)

SDCS1#

0x90000000 – 0x9FFFFFFF

32-bit

SDRAM (U41/U49)

UART and CPLD address map

PXA270 chip select Physical address Bus

width

Description

0x10000000 – 0x107FFFFE

16-bit

0x10800000 – 0x10FFFFFE

16-bit

0x11000000 – 0x117FFFFE

16-bit

0x11800000 – 0x11FFFFFE

16-bit

0x12000000 16-bit

0x12800000 16-bit

0x13000000 16-bit

CS4#

0x13800000 16-bit

1

Details of the internal registers are in the Intel PXA27x Processor Family Developer’s

Manual

on the Development Kit CD.