Pci-to-isa bridge (pib), Super i/o, Isa dma channels – Emerson I/O MODULE IPMC7126E User Manual

Page 35: Z8536 cio port pins, Table 3-7. strap pins configuration, Table 3-8. pib dma channel assignments

Chapter 3 Programming

IPMC7126E/7616E I/O Module Installation and Use (6806800A45B)

21

PCI-to-ISA Bridge (PIB)

The PIB contains ISA Bridge I/O Registers for various functions. These registers are accessible

from the PCI bus.

Super I/O

The Super I/O device provides the following functions:

■

Two serial ports (asynchronous)

■

Parallel port interface

The device’s hardware configuration is based on two strap-pins: BADDR0 and BADDR1. During

reset, strapping options shown on BADDR0 and BADDR1 pins determine the device’s

operation. Clock speed is 48 MHz.The following table shows the hardware strapping for the

Super I/O device:

ISA DMA Channels

The following table lists PIB DMA Channel Assignments not used.

Z8536 CIO Port Pins

The following table lists port pins not used by the IPMC761 module.

Notes

1.

The Hawk External Register Set interface now provides these functions.

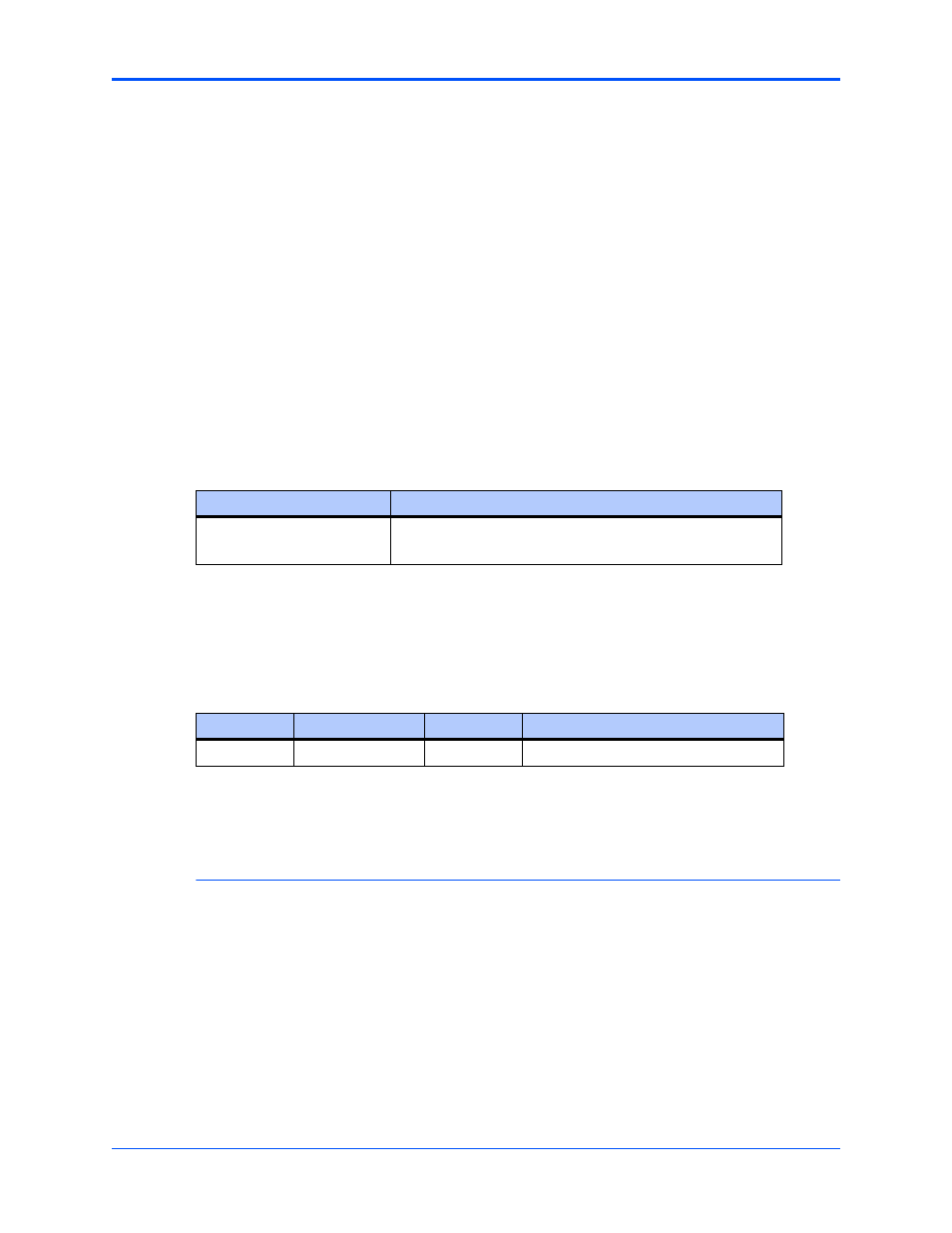

Table 3-7. Strap Pins Configuration

Pins

Reset Configuration

BADDR1

BADDR0

1,1 - Index Register 002Eh, Data Register 002Fh,

PnP motherboard mode,Wake up in Config state

Table 3-8. PIB DMA Channel Assignments

PIB Priority

PIB Label

Controller

DMA Assignment

Highest

Channel 2

DMA1

Not used on module