Memory control – load start address, Memory control – size burst, Memory control – load data for memory – Sundance SMT377 User Manual

Page 19: Memory control – read from memory \(address\)

Version 1.1

Page 19 of 22

SMT377 User Manual

100KHz). The maximum value of the shift register is 16383, giving a sampling

frequency of 1.22 KHz.

For instance, to generate a 50KHz clock, you need to load the shift register with the

following value: 20,000 / 50 = 400.

The shift register can be reloaded at any time. It is internally updated after the

completion of an entire cycle of the previous value, in order to avoid jumps or un-

wanted output value. It can also be updated while the Pattern Generator is running.

Shift Register 0 (Channels 1, 2, 3 and 4) and 1 (Channels 5, 6, 7 and 8) can be

loaded with different value when using the Direct Transfer mode (samples received

by ComPort routed directly to DAC). When using the Pattern Generator mode, it is

required to have the same value for both Shift Register, if not, Shift Register 1 is

ignored and is overridden by Shift Register 0. This is due to the current version of the

firmware that implements only one ZBTRAM interface.

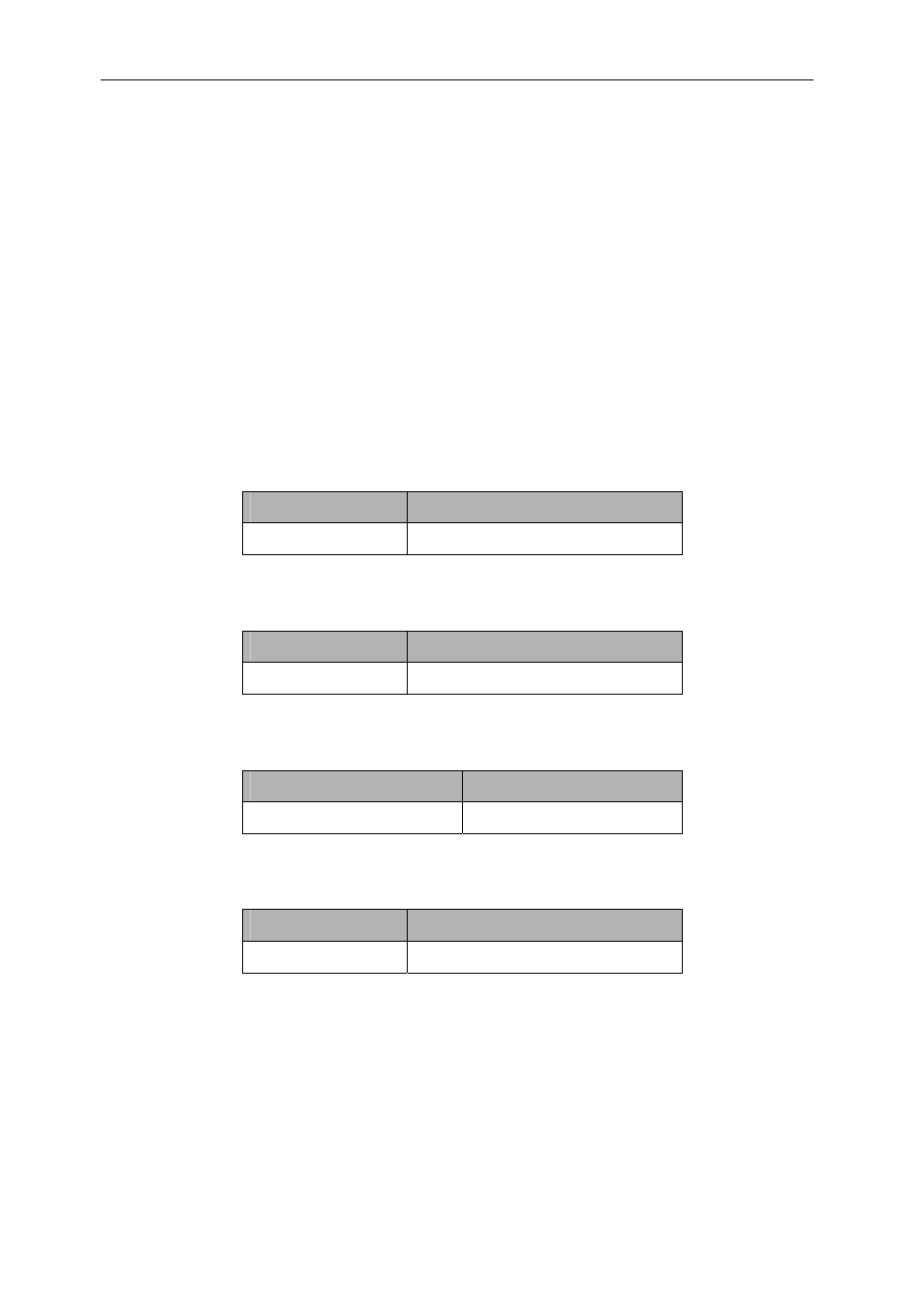

Memory Control – Load start address.

27…21

20…0

Not used.

Start address

Memory Control – Size burst.

27…21

20…0

Not used.

Burst size

Memory Control – Load data for memory.

27…16

15…0

Not used.

Sample data

Memory Control – Read from memory (address).

27…21

20…0

Not used.

Read address

When sending an address in this mode, the sample data stored at this location is

sent back via the control CommPort 3.