Sundance SMT370v2 User Manual

Page 42

Version 2.0

Page 42 of 46

SMT370v2/v3 User Manual

Register 0xD – FPGA Global Reset.

By sending this control word, the FPGA gets reset. Every single register in the FPGA

is reset. The FPGA transmit that command to the:

- DAC, which will need to be reconfigured,

- Clock synthesizers, which keep the internal register values but does not output

any signal,

- Clock multiplexers, which take there default state (external clocks routed to

FPGA, DAC and ADCs)

- The interface implemented in the FPGA, including ComPort interface. It is note

recommended to proceed to an FPGA global reset while communications are

happening. It might stick the other end into an unknown state.

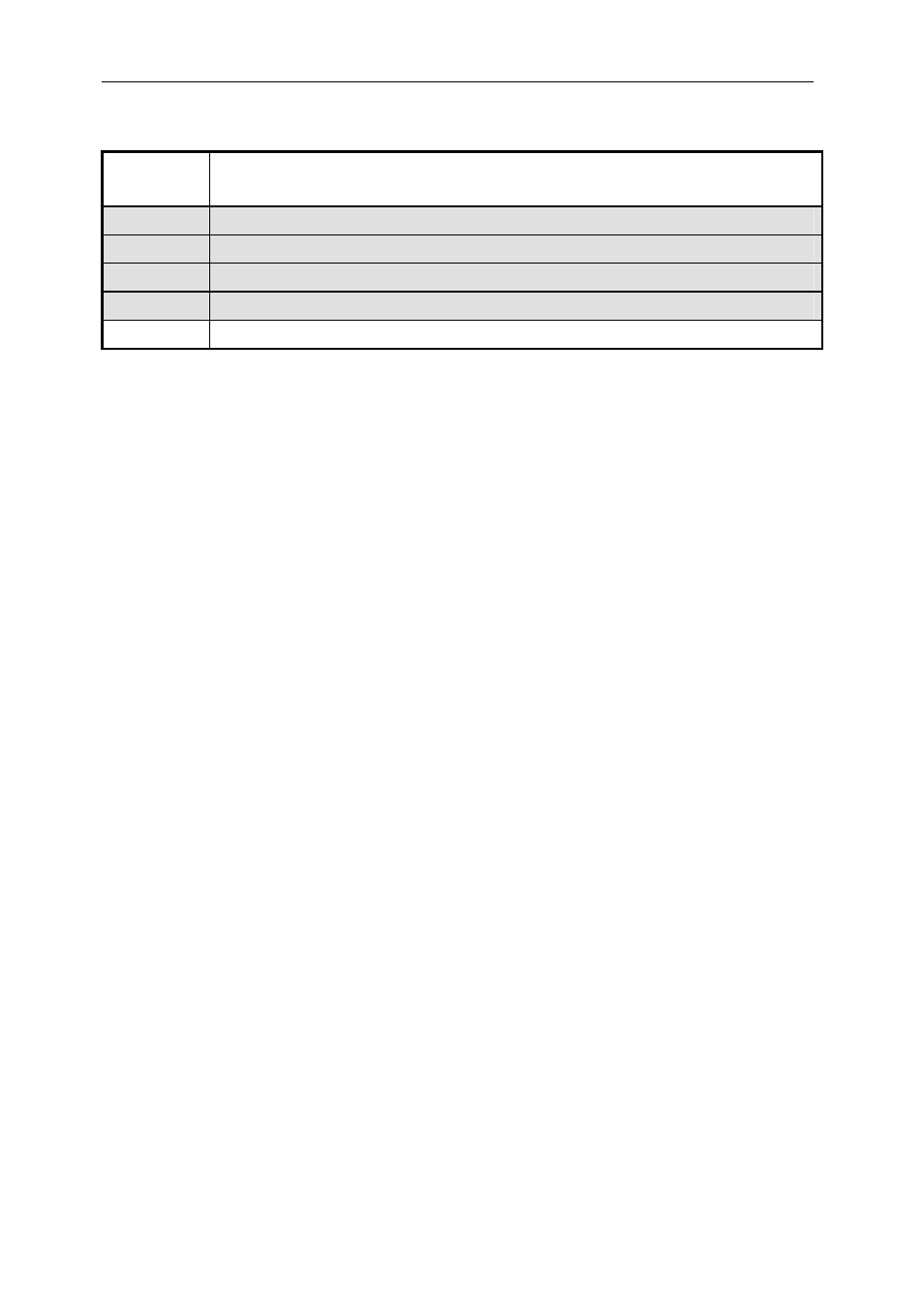

Bit

number

Description

Bit 31

1

Bit 30

1

Bit 29

0

Bit 28

1

Bit 27-0

Not Used.