Measurement Computing PPIO-AI08 User Manual

Page 14

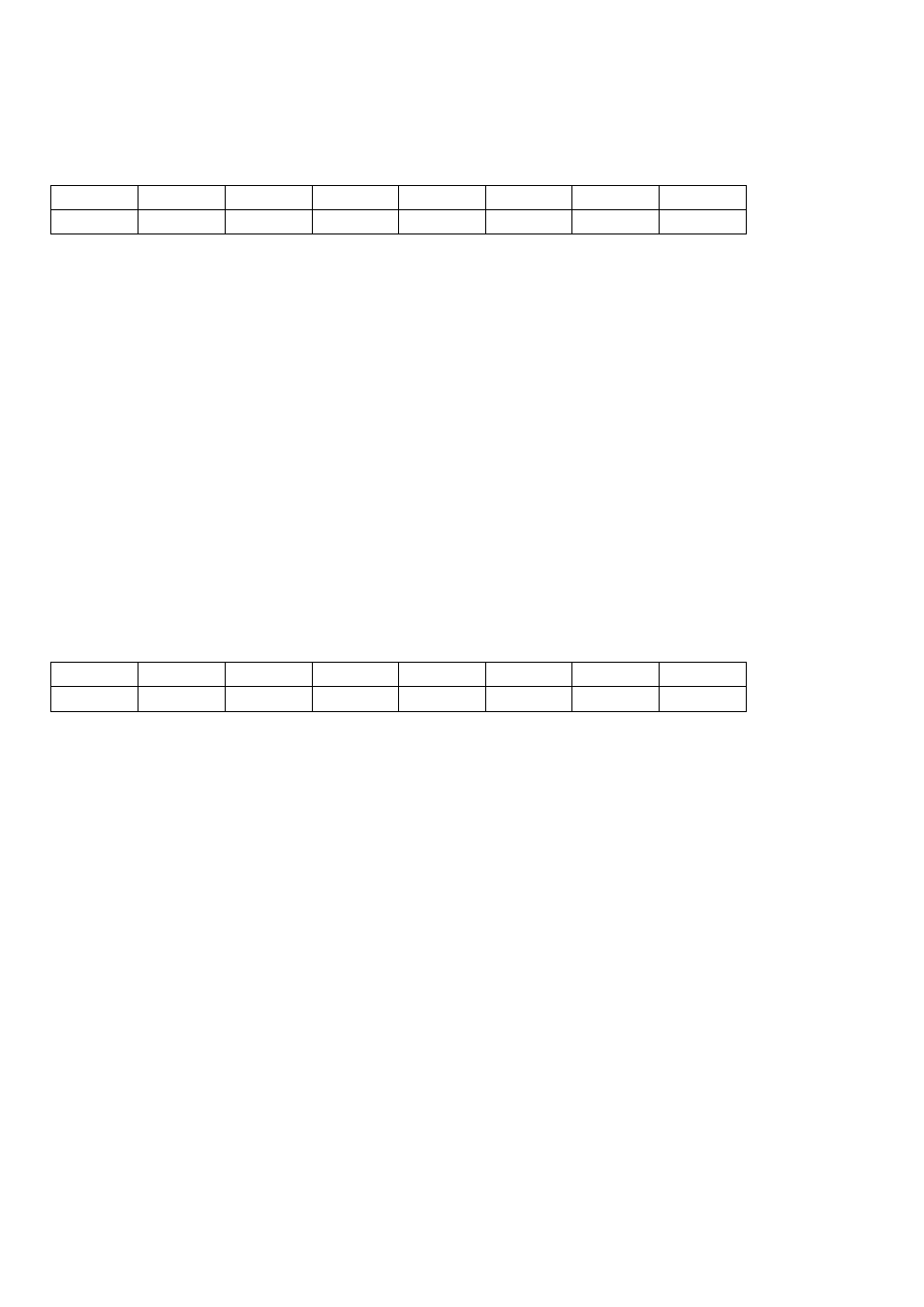

5.3.2 Status And Control Register

BASE + 2

This register address is two registers, one is read-active and one is write-active.

MUX0

MUX1

MUX2

IRQ

IP1

IP2

IP3

EOC

0

1

2

3

4

5

6

7

READ =

STATUS

EOC = 1, the A/D is busy converting and data should not be read.

EOC = 0, the A/D is not busy and data can be read.

IP3 to IP1 are the digital input lines (DI#) on the 37-pin I/O connector.

IRQ is the status of an edge triggered latch connected to pin 24 of the analog

connector. It is high (1) when a positive edge has been detected. It can be reset to 0 by

writing to the

INTE

mask at

BASE

+ 2 write.

MUX 2 to

MUX

0 is the current multiplexer channel. The current channel is a binary-

coded number between 0 and 7 .

WRITE =

CONTROL

MUX0

MUX1

MUX2

NA

OP1

OP2

OP3

OP4

0

1

2

3

4

5

6

7

OP4 to OP1 are the digital output (DO#) lines on the 37-pin I/O connector.

NA = Not Applicable. On a CIO-DAS8, this bit controls the passing of interrupts into

the

PC

bus. The

PPIO

does not reside on the bus and does not have access to

interrupts.

MUX2 to MUX0. Set the current channel address by writing a binary coded number

between 0 and 7 to these three bits.

NOTE

Every write to this register sets the current A/D channel

MUX

setting to the number in bits 2-0.

10