Measurement Computing PCI-DIO48H/CTR15 User Manual

Page 14

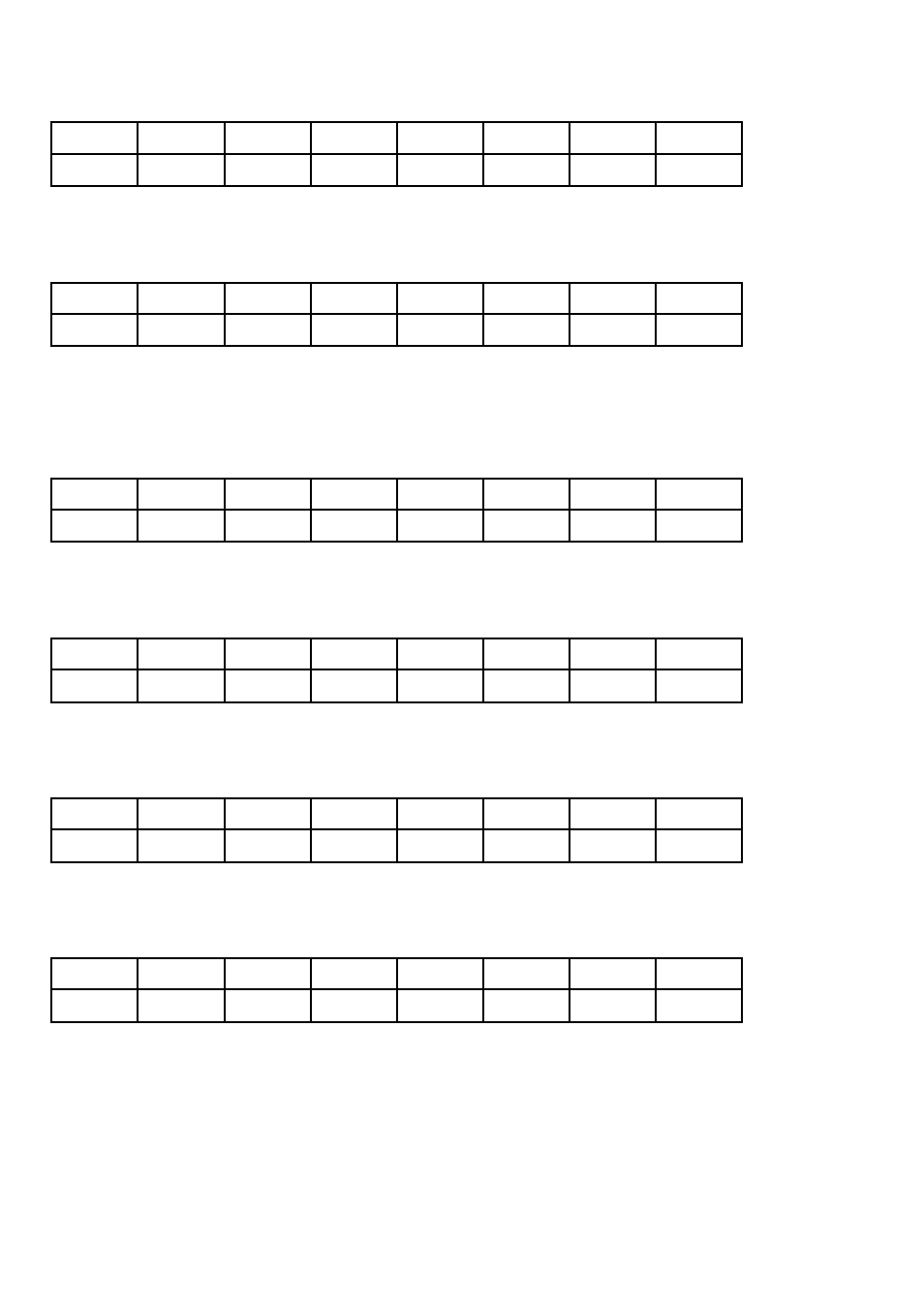

PORT 2C DATA

BADR2 + 06h

READ/WRITE

CL0

CL1

CL2

CL3

CH0

CH1

CH2

CH3

0

1

2

3

4

5

6

7

CONTROL REGISTER 2

BADR2 + 07h

WRITE only

D0

D1

-

D3

D4

-

-

-

0

1

2

3

4

5

6

7

See BADR2 + 03h and Table 5-2 for a description of the Control Register.

COUNTER 1 DATA

BADR2 + 08h

READ/WRITE

D0

D1

D2

D3

D4

D5

D6

D7

0

1

2

3

4

5

6

7

COUNTER 2 DATA

BADR2 + 09h

READ/WRITE

D0

D1

D2

D3

D4

D5

D6

D7

0

1

2

3

4

5

6

7

COUNTER 3 DATA

BADR2 + 0Ah

READ/WRITE

D0

D1

D2

D3

D4

D5

D6

D7

0

1

2

3

4

5

6

7

CONTROL REGISTER COUNTERS 1 - 3

BADR2 + 0Bh

WRITE ONLY

D0

D1

D2

D3

D4

D5

D6

D7

0

1

2

3

4

5

6

7

The control register is used to set the operating Modes of 8254 Counters 0,1 & 2. A

counter is configured by writing the correct Mode information to the Control

Register, then the proper count data must be written to the specific Counter Register.

The Counters on the 8254 are 16-bit devices. Since the interface to the 8254 is only

8-bits wide, Count data is written to the Counter Register as two successive bytes.

10

- ACC-300 (7 pages)

- AI-EXP32 (20 pages)

- AI-EXP48 (19 pages)

- BTH-1208LS (30 pages)

- 6K-ERB08 (32 pages)

- BTH-1208LS Quick Start (4 pages)

- 6K-SSR-RACK08 (33 pages)

- BTH-1208LS-OEM (27 pages)

- CB-COM-Digital (68 pages)

- CB-7018 (68 pages)

- CB-7000 Utilities (44 pages)

- CB-7080D (74 pages)

- CB-COM-7033 (44 pages)

- CB-COM-7017 (72 pages)

- CB-COM-7024 (76 pages)

- CB-NAP-7000P (36 pages)

- CIO-DAC02/16 (16 pages)

- CIO-DAC02 (18 pages)

- CB-NAP-7000D (56 pages)

- CIO-DAC16-I (16 pages)

- CIO-DAC16/16 (20 pages)

- CIO-DAS08 (21 pages)

- CIO-DAC16 (20 pages)

- CIO-DAS08/JR (16 pages)

- CIO-DAS08/JR/16 (14 pages)

- CIO-DAS08/JR-AO (16 pages)

- CIO-DAS08-AOM (32 pages)

- CIO-DAS08-PGM (28 pages)

- CIO-DAS16/330 (34 pages)

- CIO-DAS48-I (17 pages)

- CIO-DAS16/M1 (38 pages)

- CIO-DAS48-PGA (18 pages)

- CIO-DAS800 (20 pages)

- CIO-DAS802/16 (22 pages)

- CIO-DAS6402/16 (40 pages)

- CIO-DAS-TEMP (20 pages)

- CIO-DDA06/16 (18 pages)

- CIO-DDA06/JR (17 pages)

- CIO-DIO24H (20 pages)

- CIO-DIO24/CTR3 (21 pages)

- CIO-DI192 (24 pages)

- CIO-DDA06 (21 pages)

- CIO-DIO48 (19 pages)

- CIO-DO192H (16 pages)

- CIO-DIO192 (20 pages)