Measurement Computing ADAC/5500 Series Installation User Manual

Page 11

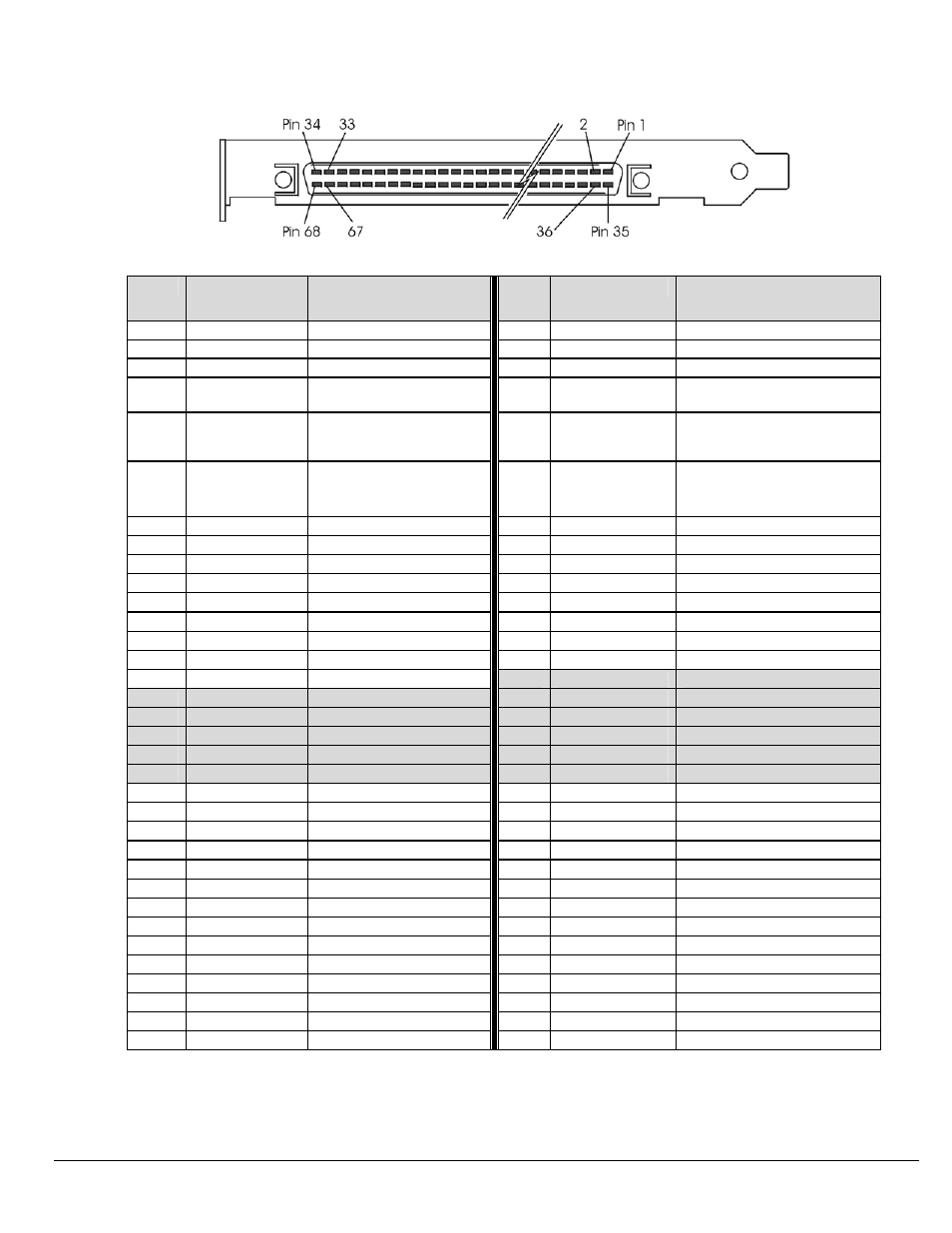

J1 Pin Assignments for ADAC/5501MF, ADAC/5502MF, ADAC/5503HR, and ADAC/5504HR

Standard 68-Pin SCSCI Type III, Socket (Female) Connector with Orb

Pin

Signal

Description / Comments

Pi

n

Signal

Description / Comments

1

DGND

Digital Ground

35

+5 V (fused)

Power

2 +15

V

(fused) Power 36

+5

V

(fused)

Power

3

-15 V (fused)

Power

37

+5 V (fused)

Power

4

ADTGOUT / TMR0

Internal ADC Trigger Output /

Timer 0 Clock Output

38

ADTGIN

External Gate (level controlled),

or External Trigger (edge active)

5 ADCLKOUT

/

TMR1

Internal ADC Trigger Output /

Timer 1 Clock Output

39

ADCLKIN / CNTR0

External ADC Clock In, or

Counter 0. Rising or Falling Edge

Sensitive.

6

DATRIGIN

DAC0 External Gate (Level

Controlled), or External

Trigger ( Edge Active)

40

DACLKIN / CNTR1

External ADC Clock In, or

Counter 0. Rising or Falling Edge

Sensitive.

7

DIO_15

TTL Level Digital I/O Ch. 15

41

DIO_14

TTL Level Digital I/O Ch. 14

8

DIO_13

TTL Level Digital I/O Ch. 13

42

DIO_12

TTL Level Digital I/O Ch. 12

9

DIO_11

TTL Level Digital I/O Ch. 11

43

DIO_10

TTL Level Digital I/O Ch. 10

10

DIO_9

TTL Level Digital I/O Ch. 9

44

DIO_8

TTL Level Digital I/O Ch. 8

11

DIO_7

TTL Level Digital I/O Ch. 7

45

DIO_6

TTL Level Digital I/O Ch. 6

12

DIO_5

TTL Level Digital I/O Ch. 5

46

DIO_4

TTL Level Digital I/O Ch. 4

13

DIO_3

TTL Level Digital I/O Ch. 3

47

DIO_2

TTL Level Digital I/O Ch. 2

14

DIO_1

TTL Level Digital I/O Ch. 1

48

DIO_0

TTL Level Digital I/O Ch. 0

15 DGND

Digital

Ground

49

CJ2

Reserved

16

CJ1

Reserved

50

CJ0

Reserved

17

MUX7

Reserved

51

MUX6

Reserved

18

MUX5

Reserved

52

MUX4

Reserved

19

MUX3

Reserved

53

MUX2

Reserved

20

MUX1

Reserved

54

MUX0

Reserved

21

AGND

Analog Ground

55

AGND

Analog Ground

22

ADEX_LO

Reserved, AD Expansion LO

56

ADEX_HI

Reserved, AD Expansion HI

23

SGND

Signal Ground

57

PDIN

Pseudo-Differential Input return

24

AIN_15

Analog Input, Ch. 15

58

AIN_7

Analog Input, Ch. 7

25

AIN_14

Analog Input, Ch. 14

59

AIN_6

Analog Input, Ch. 6

26

AIN_13

Analog Input, Ch. 13

60

AIN_5

Analog Input, Ch. 5

27

AIN_12

Analog Input, Ch. 12

61

AIN_4

Analog Input, Ch. 4

28

AIN_11

Analog Input, Ch. 11

62

AIN_3

Analog Input, Ch. 3

29

AIN_10

Analog Input, Ch. 10

63

AIN_2

Analog Input, Ch. 2

30

AIN_9

Analog Input, Ch. 9

64

AIN_1

Analog Input, Ch. 1

31

AIN_8

Analog Input, Ch. 8

65

AIN_0

Analog Input, Ch. 0

32

RTN1

Voltage output return, line 1.

66

DAC1 (Note 2)

Digital-to-Analog Converter 1

33

RTN0

Voltage output return, line 0.

67

DAC0 (Note 1)

Digital-to-Analog Converter 0

34

AGND

Analog Ground

68

DGND

Digital Ground

Note 1: The clock source of the primary DAC0 channel may be software command, DAC0 Pacer clock,

or an external event (DACLKIN).

Note 2: The clock source of the secondary DAC1 channel may be software command, DAC1 Pacer clock,

or Channel 0 clock source.

1107-0940, rev 2.0

908096

ADAC/5500 Series Installation Guide 11