D/a external timebase signal, General-purpose counter signal timing, Ctr1 clk signal – Measurement Computing PCI-DAS6013 User Manual

Page 26

PCI-DAS6013 and PCI-DAS6014 User's Guide

Functional Details

26

D/A EXTERNAL TIMEBASE signal

The D/A EXTERNAL TIME BASE signal can serve as the source for the on-board DAC pacer circuit rather

than using the internal time base. Any AUXIN pin can be set programmatically as the source for this signal. The

polarity is programmable.

The maximum frequency for the D/A EXTERNAL TIMEBASE signal is 20 MHz. The minimum pulse width is

23 ns high or low. There is no minimum frequency specification.

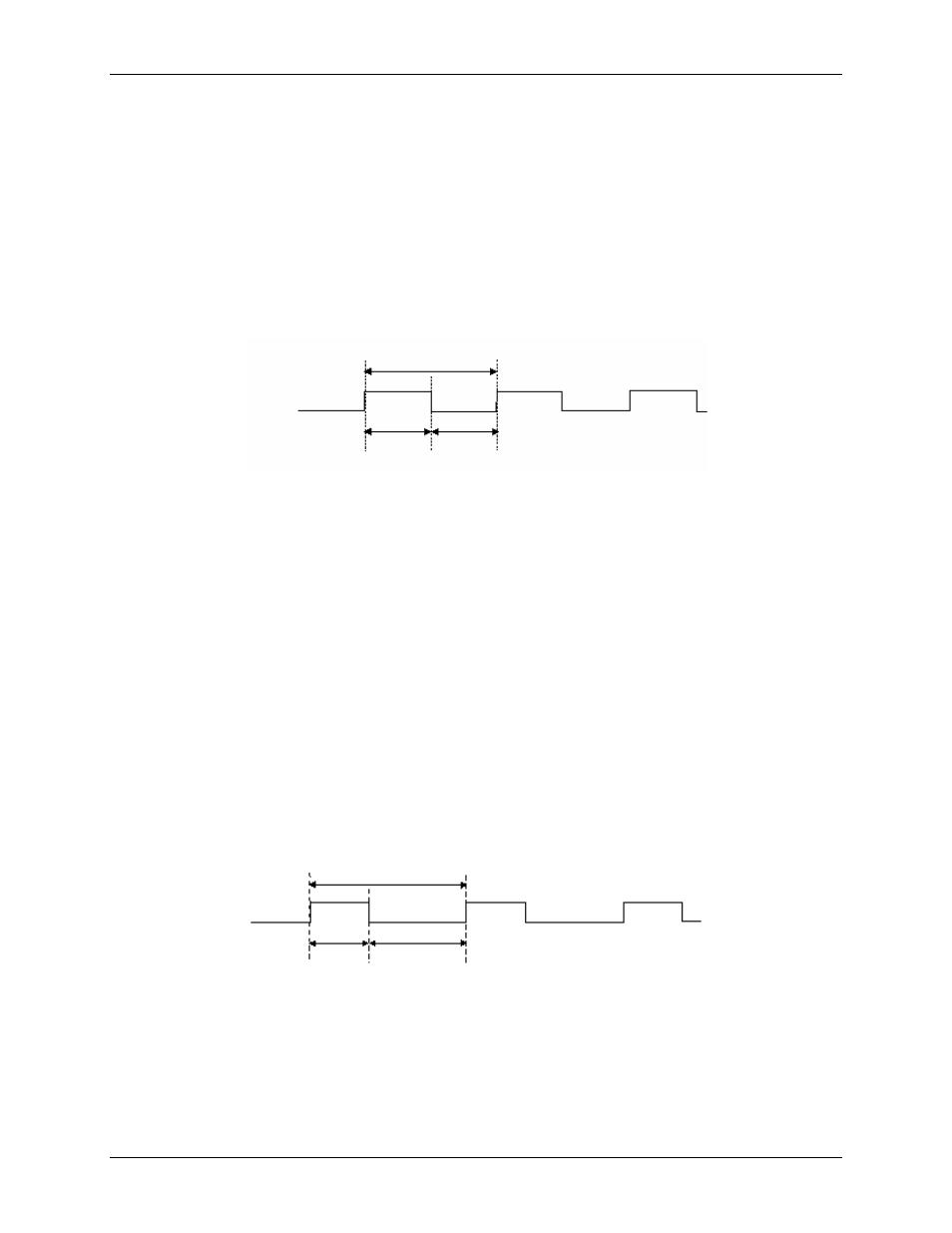

Figure 21 shows the timing requirements for the D/A EXTERNAL TIMEBASE signal.

t

w

t

w

=23 ns minimum

t

p

t

w

t

p

=50 ns minimum

Figure 21. D/A EXTERNAL TIMEBASE signal timing

General-purpose counter signal timing

The general-purpose counter signals are:

CTR1 CLK

CTR1 GATE

CTR1 OUT

CTR2 CLK

CTR2 GATE

CTR2 OUT

CTR1 CLK signal

The CTR1 CLK signal can serve as the clock source for independent user counter 1. It can be selected through

software at the CTR1 CLK pin rather than using the on-board 10 MHz or 100 kHz sources. It is also polarity

programmable. The maximum input frequency is 10 MHz. There is no minimum frequency specified. Figure 22

shows the timing requirements for the CTR1 CLK signal.

t

w-L

t

w-H

=15 ns minimum

t

w-H

t

p

=100 ns minimum

t

w-L

=25 ns minimum

Figure 22. CTR1 CLK signal timing