Measurement Computing CIO-DAS800 User Manual

Page 15

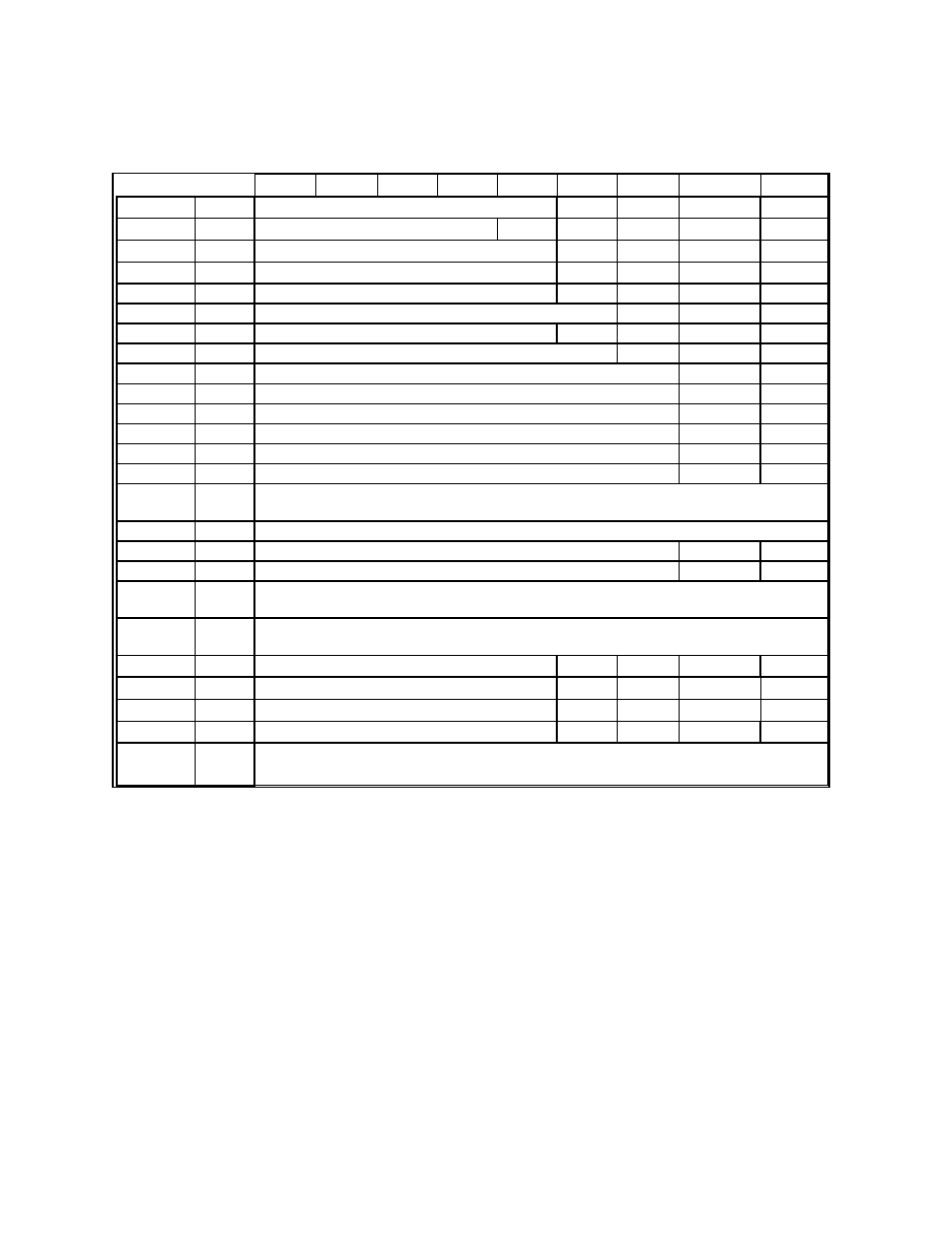

Table 4-3. Bit Definitions

* Asterisk indicates that HCEN is required (as a final step) to make

this bit functional.

Digital Output bits

.

W

OP4:1

Digital Input bits.

R

IP3:1

Channel-scan end value

W

EC2:0*

Channel-scan start value.

W

SC2:0*

0 if HCEN =0. 0 if HCEN =1 & FIFO not empty. Undefined if HCEN = 1 and FIFO

empty

R

FF3*

0 if HCEN =0. 0 if HCEN =1 & FIFO not empty. Undefined if HCEN = 1 and FIFO

empty

R

FF2*

FIFO Overflow (full) =1. 0 if HCEN =0.

R

FFOV*

FIFO Empty =1. 0 if HCEN =0.

R

FFEM*

State of Digital Trigger (1=Trigger occured)

R

DT*

Enable Interrupt on FIFO Half Full (Req. IEOC=1, HCEN must =1 to enable

FIFO)

W

ENHF*

(N/A)

RW

R3:0

Register Selection (See Table Below)

W

CS1:0

Register Select Enable/Range Select Disable

W

CSE

Internal Time Base (8254) Enable

RW

ITE*

Cascade AD Pacing Mode Enable (include CT/2)

RW

CASC*

External Digital Trigger Enable (Edge trig if GTEN=0)

RW

DTEN*

Interrupt Source (1 = End of Convert, 0 = Ext)

RW

IEOC

Enable Auto channel-scan

RW

EACS*

Gate Enable (Req. DTEN to enable HW gate)

RW

GTEN*

Hardware Convert Enable

RW

HCEN

End-of-conversion (1 = busy, 0 = ready)

R

EOC

Interrupt enable (0 = disable, 1 = enable)

RW

INTE

Mux address bits

RW

MA2:0

Analog data input (Read low byte first)

R

AD 11:0

DEFINITIONS:

11