Measurement Computing CIO-DAS800 User Manual

Page 12

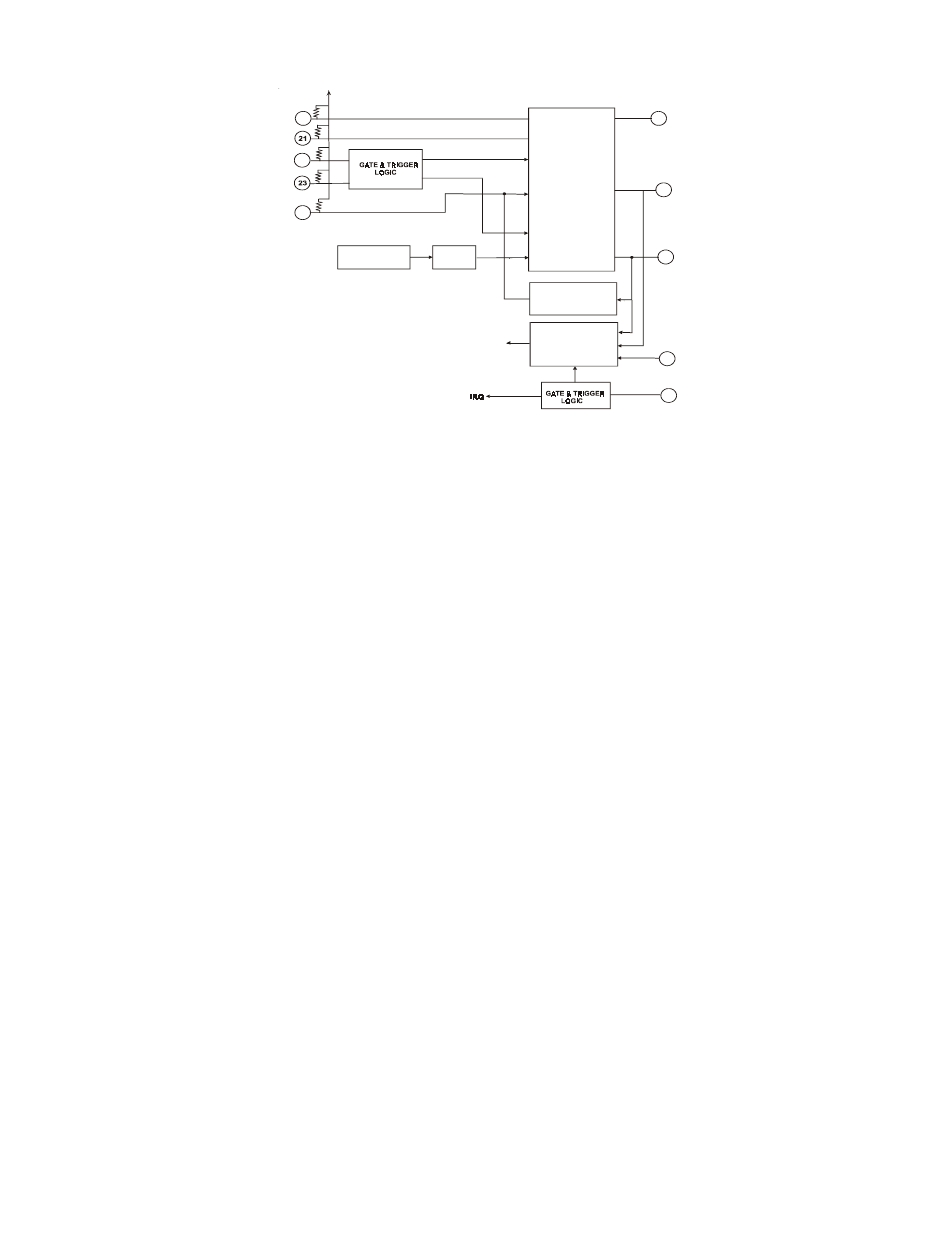

Figure 1-1. Counter/Timer Functional Diagram

Figure 1-1 shows the 82C54 functions, I/O pins and how these are connected on the CIO-DAS800.

The CIO-DAS800 CTR2 input is connected to the PC bus clock/2 or the 1 MHz. crystal signal. The

system default is the PC bus clock.

Software controls the counters that generate the A/D pacing pulse.

Note: A/D conversions are triggered by falling-edge signals. The pulses generated by the 82C54 are

low-going for one count length. The A/D is triggered as the signal goes low. Any A/D trigger signal you

supply externally must also be low-going at the desired moment of A/D conversion.

8

10 M H Z C RYS TA L

O S CILLATO R

D IV ID E B Y

10

C LK 2

C LK 1

C LK 0

C ASC A DE

C O NTR O L

LO G IC

PAC ER

C O NTR O L

LO G IC

O U T 0

O U T 1

O U T 2

C TR 0 O U T

C TR 1 O U T

C TR 2

O UT

+5V DC

+5V DC

A LL

10K

2

4

G ATE 0

G ATE 1

G ATE 2

22

INT INP UT /

XC LK

25

D IN 1/

TRIG

24

6

5

3

82C 54

STA RT CO N VE RT

- ACC-300 (7 pages)

- AI-EXP32 (20 pages)

- AI-EXP48 (19 pages)

- BTH-1208LS (30 pages)

- 6K-ERB08 (32 pages)

- BTH-1208LS Quick Start (4 pages)

- 6K-SSR-RACK08 (33 pages)

- BTH-1208LS-OEM (27 pages)

- CB-COM-Digital (68 pages)

- CB-7018 (68 pages)

- CB-7000 Utilities (44 pages)

- CB-7080D (74 pages)

- CB-COM-7033 (44 pages)

- CB-COM-7017 (72 pages)

- CB-COM-7024 (76 pages)

- CB-NAP-7000P (36 pages)

- CIO-DAC02/16 (16 pages)

- CIO-DAC02 (18 pages)

- CB-NAP-7000D (56 pages)

- CIO-DAC16-I (16 pages)

- CIO-DAC16/16 (20 pages)

- CIO-DAS08 (21 pages)

- CIO-DAC16 (20 pages)

- CIO-DAS08/JR (16 pages)

- CIO-DAS08/JR/16 (14 pages)

- CIO-DAS08/JR-AO (16 pages)

- CIO-DAS08-AOM (32 pages)

- CIO-DAS08-PGM (28 pages)

- CIO-DAS16/330 (34 pages)

- CIO-DAS48-I (17 pages)

- CIO-DAS16/M1 (38 pages)

- CIO-DAS48-PGA (18 pages)

- CIO-DAS802/16 (22 pages)

- CIO-DAS6402/16 (40 pages)

- CIO-DAS-TEMP (20 pages)

- CIO-DDA06/16 (18 pages)

- CIO-DDA06/JR (17 pages)

- CIO-DIO24H (20 pages)

- CIO-DIO24/CTR3 (21 pages)

- CIO-DI192 (24 pages)

- CIO-DDA06 (21 pages)

- CIO-DIO48 (19 pages)

- CIO-DO192H (16 pages)

- CIO-DIO192 (20 pages)