Diamond Systems Rhodeus-LC LX800 PC/104 User Manual

Page 33

- 30 -

BIOS

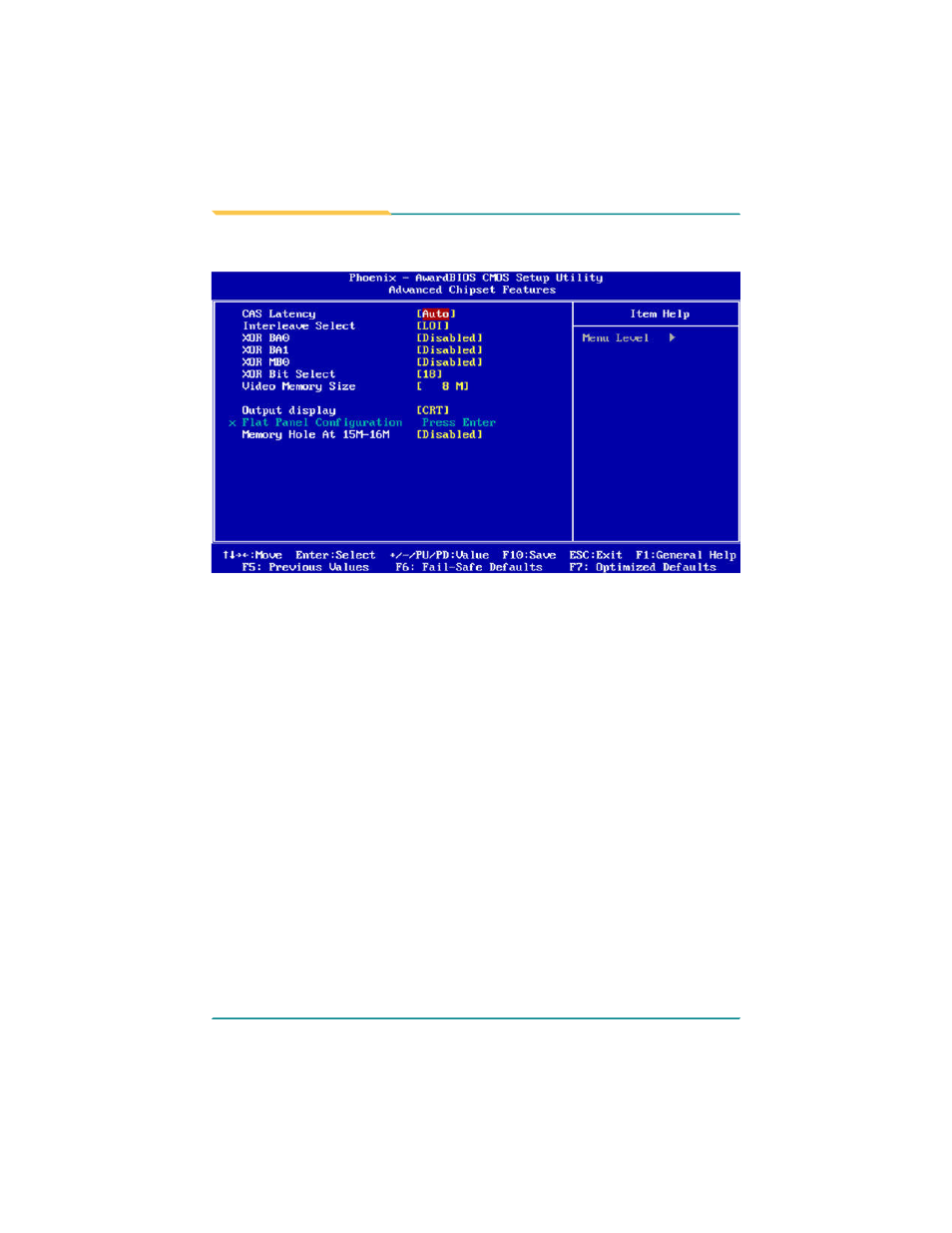

3.5 Advanced Chipset Features

CAS Latency Time

It allows CAS latency time in HCLKs as 2 or 2.5. The system board designer

VKRXOGVHWWKHYDOXHVLQWKLV¿HOGGHSHQGLQJRQWKH'5$0LQVWDOOHG'R

QRWFKDQJHWKHYDOXHVLQWKLV¿HOGXQOHVV\RXFKDQJHVSHFL¿FDWLRQVRIWKH

installed DRAM or CPU.

Setting: 2.5 (Default), 2.

Interleave Select

It allows you to Use the Interleave Select option to specify how the cache

memory is interleaved.

Setting: LOI (Default), HOI.

XOR BA0

Setting: Disabled (Default), Enabled.

XOR BA1

Setting: Disabled (Default), Enabled.