Delta DT3 User Manual

Page 20

20

selection

0812H

Decimal point position selection

0: No decimal place 1: decimal place. (Except for the thermocouple B,S,R type,

all other thermocouple type are valid.)

0813H

AT setting

OFF: 0 (default), ON : 1

0814H

Control RUN/STOP setting

0: STOP, 1: RUN (default)

0815H

STOP setting for PID program

control

0: RUN (default), 1: STOP

0816H

Temporarily STOP for PID program

control

0: RUN (default), 1: Temporarily STOP

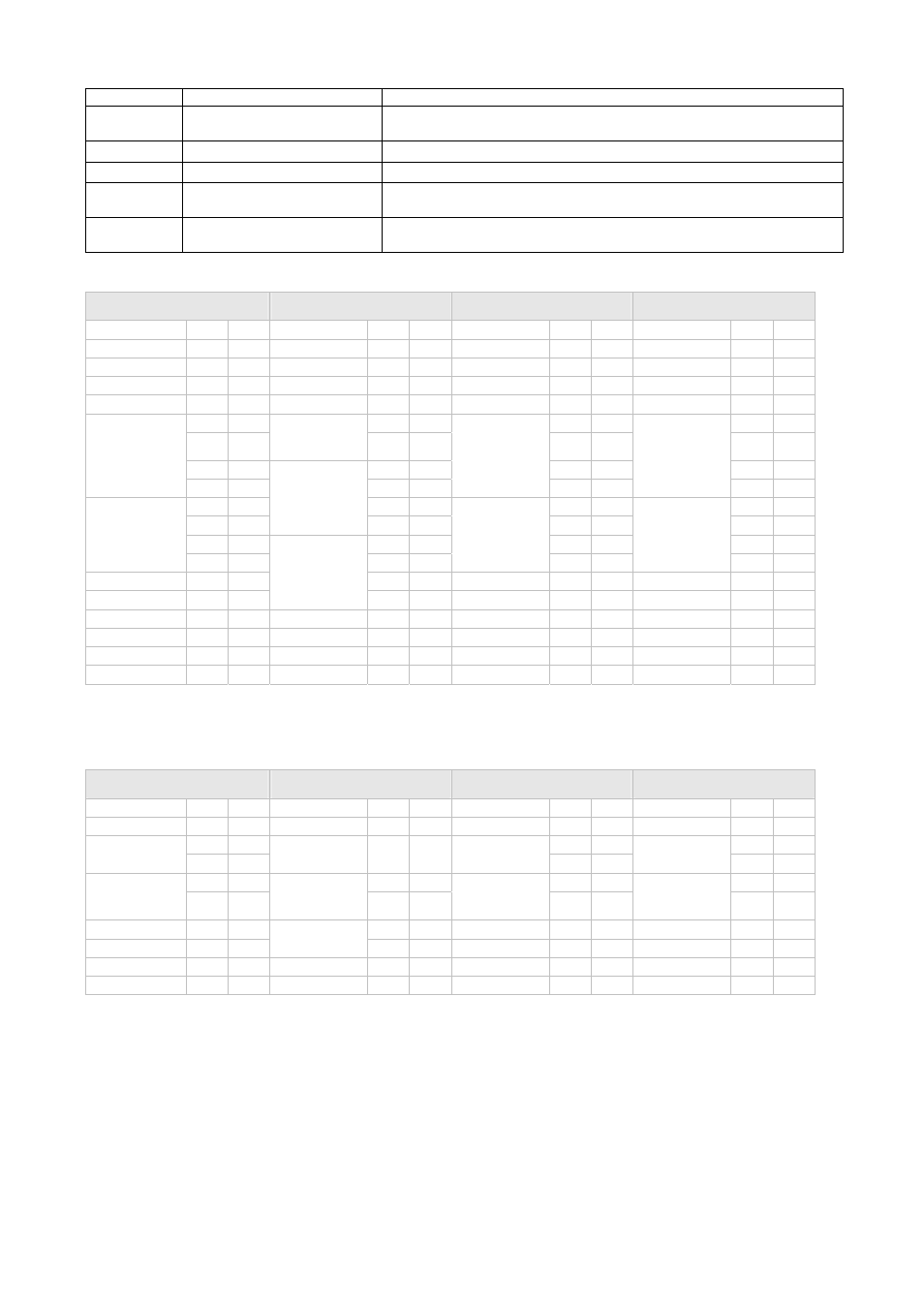

2. Communication Transmission Format: Command Code: 02: read bits, 05: write bit, 03: read words, 06: write 1 word

ASCII Mode

Read Command

Read Command Response

Write Command

Write Command Response

STX

’: ’

’: ’

STX

’: ’

’: ’

STX

’: ’

’: ’

STX

’: ’

’: ’

ADR

1 ‘0’

‘0’ ADR

1 ‘0’

‘0’ ADR

1 ‘0’

‘0’ ADR

1 ‘0’

‘0’

ADR

0 ‘1’

‘1’ ADR

0 ‘1’

‘1’ ADR

0 ‘1’

‘1’ ADR

0 ‘1’

‘1’

CMD

1 ‘0’

‘0’ CMD

1 ‘0’

‘0’ CMD

1 ‘0’

‘0’ CMD

1 ‘0’

‘0’

CMD

0 ‘3’

‘2’ CMD

0 ‘3’

‘2’ CMD

0 ‘6’

‘5’ CMD

0 ‘6’

‘5’

‘1’ ‘0’

‘0’ ‘0’

‘1’ ‘0’

‘1’ ‘0’

‘0’ ‘8’

Number of data

(count by byte)

‘4’ ‘2’

‘0’ ‘8’

‘0’ ‘8’

‘0’ ‘1’

‘0’ ‘1’

‘0’ ‘1’

‘0’ ‘1’

Starting data

address

‘0’ ‘0’

‘1’ ‘7’

Starting data

address

‘1’ ‘0’

Starting data

address

‘1’ ‘0’

‘0’ ‘0’

‘F’ ‘0’

‘0’ ‘F’

‘0’ ‘F’

‘0’ ‘0’

Start address

data

1000H/081xH

‘4’ ‘1’

‘3’ ‘F’

‘3’ ‘F’

‘0’ ‘0’

‘0’

‘E’ ‘0’

‘E’ ‘0’

Number of data

(word/Bit)

‘2’ ‘9’

‘0’

Data content

‘8’ ‘0’

Data content

‘8’ ‘0’

LRC 1

‘E’

‘D’

‘0’

LRC1

‘F’

‘E’

LRC1

‘F’

‘E’

LRC 0

‘A’

‘C’

Address data

1001H

‘0’

LRC 0

‘D’

‘3’

LRC 0

‘D’

‘3’

END 1

CR

CR

LRC 1

‘0’

‘E’

END 1

CR

CR

END 1

CR

CR

END 0

LF

LF

LRC 0

‘3’

‘3’

END 0

LF

LF

END 0

LF

LF

END

1

CR

CR

END

0

LF

LF

LRC checksum:

LRC check is the added sum from “Address” to “Data content”. For example, 01H + 03H + 10+ 00H + 00H + 02H = 16H, then take the

complementary of 2, EAH.

RTU Mode

Read Command

Read Command Response

Write Command

Write Command Response

ADR 01H

01H ADR 01H

01H

ADR 01H

01H

ADR 01H

01H

CMD 03H

02H CMD 03H

02H

CMD 06H

05H

CMD 06H

05H

10H 08H

10H

08H

10H 08H

Starting data

address

00H 10H

Number of data

(count by byte)

04H

02H

Starting data

address

01H

10H

Starting data

address

01H 10H

00H 00H

01H

17H

03H

FFH

03H FFH

Number of data

(word/Bit)

02H 09H

Start address

data

1000H/081xH

F4H

01H

Data content

20H

00H

Data content

20H 00H

CRC 1

C0H BBH

03H

CRC 1

DDH

8FH

CRC 1

DDH

8FH

CRC 0

CBH A9H

Address

data1001H

20H

CRC 0

E2H

9FH

CRC 0

E2H

9FH

CRC

1 BBH

77H

CRC

0 15H

88H

CRC (Cyclical Redundancy Check) is obtained by the following steps.

1. Load in a 16-bit register FFFFH as the CRC register.

2. Do an exclusive OR operation of the first byte of the data and low byte of CRC register, and place the operation result back to

the CRC register.

3. Right shift the bits in the CRC register and fill the high bits with “0”. Check the removed lowest bit.

4. If the removed lowest bit is “0”, repeat step 3. Otherwise, do an exclusive OR operation of the CRC register and the value

A001H and place the operation result back to the CRC register.

5. Repeat step 3 and 4 until the 8 bits (1 byte) are all right shifted.

6. Repeat step 2 and 5 and calcualte all the bits to obtain CRC check.

Please be aware of the high/low byte transmission order in the CRC register.