6 smbus addressing, 7 interrupt routing, 6 smbus addressing 5.7 interrupt routing – Artesyn PrAMC-7311 Installation and Use (June 2014) User Manual

Page 56: Table 5-6, Smbus addressing, Table 5-7, Interrupt routing, Address mapping

Address Mapping

PrAMC-7311 Installation and Use (6806800P34D)

56

5.6

SMBus Addressing

The following table lists the devices on the SMBusses and their addresses.

5.7

Interrupt Routing

Override default configuration parameters for the IRQ priority table. This table is used by the

PlatformCsm component and describes the list of interrupts to assign to device interrupt line

registers (0x3c). Only non-zero values are considered for IRQ assignment.

Config BOARD_PCI_IRQ_1, 11 // first valid IRQ number.

Config BOARD_PCI_IRQ_2, 10 // next valid IRQ number.

Config BOARD_PCI_IRQ_3, 9 // next valid IRQ number.

Config BOARD_PCI_IRQ_4, 0 // next valid IRQ number.

Config BOARD_PCI_IRQ_5, 0 // next valid IRQ number.

Config BOARD_PCI_IRQ_6, 0 // next valid IRQ number.

Config BOARD_PCI_IRQ_7, 0 // last valid IRQ number.

Create PCI Device objects with IRQ routing. Interrupt pin objects (i.e., PIRQA, PIRQB, etc.)

available on this system are defined in the Module.def file of the platform module.

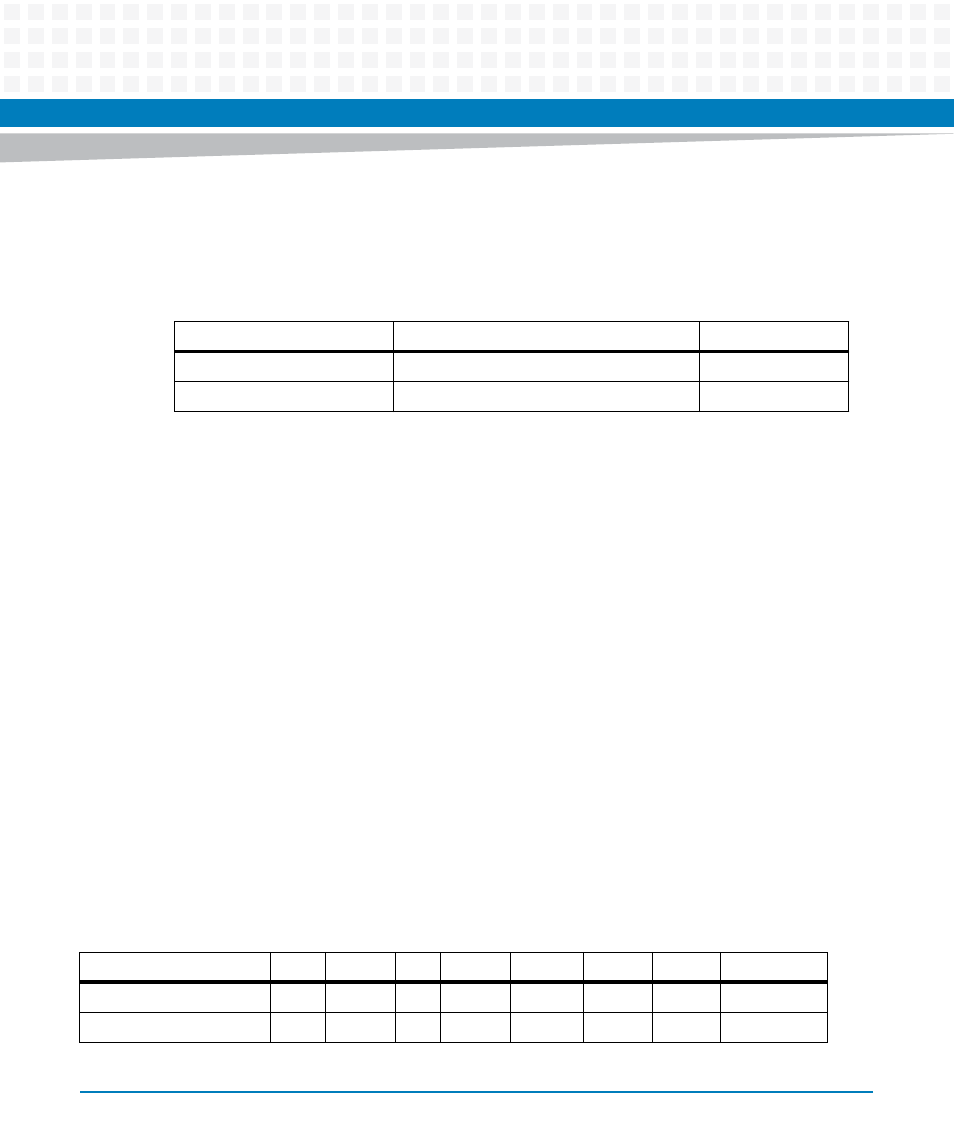

Table 5-6 SMBus Addressing

SMBus

Device

Address

SMBus 0

SPD1(U9)

0xA0

SMBus 0

SPD2(U21)

0xA4

Table 5-7 Interrupt Routing

Name

Bus

Device

Fn

PinA

PinB

PinC

PinD

Slot

PciDev IntelImc

0

0

0

PIRQA

PIRQB

PIRQC

PIRQD

PciDev PcieGfxPort

0

1

0

PIRQA

PIRQB

PIRQC

PIRQD