I2c bus, General purpose i/o (gpio), Power and system management – ADLINK Express-IB User Manual

Page 23

Express-IB

Page 23

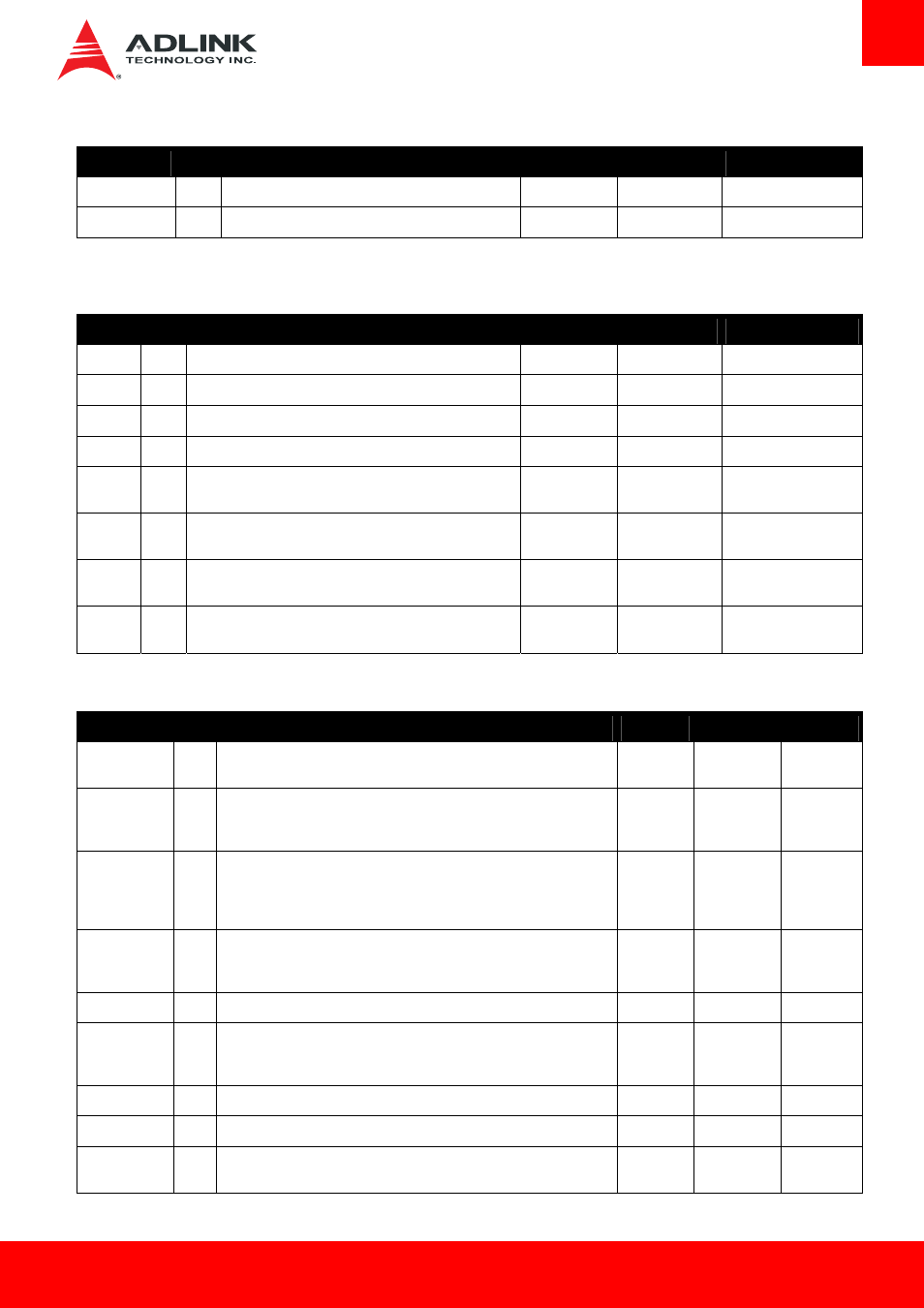

3.3.13. I2C Bus

Signal

Pin # Description

I/O

PU/PD

Comment

I2C_CK

B33

General purpose I²C port clock output/input

I/O OD 3.3VSB

PU 2k2 3.3VSB

I2C_DAT

B34

General purpose I²C port data I/O line

I/O OD 3.3VSB

PU 2k2 3.3VSB

3.3.14. General Purpose I/O (GPIO)

Signal

Pin # Description

I/O

PU/PD

Comment

GPO[0]

A93

General purpose output pins.

O 3.3V

GPO[1]

B54

General purpose output pins.

O 3.3V

GPO[2]

B57

General purpose output pins.

O 3.3V

GPO[3]

B63

General purpose output pins.

O 3.3V

GPI[0]

A54

General purpose input pins.

Pulled high internally on the module.

I 3.3V

PU 10K 3.3V

PU not in PICMG

suggest 10K

GPI[1]

A63

General purpose input pins.

Pulled high internally on the module.

I 3.3V

PU 10K 3.3V

PU not in PICMG

suggest 10K

GPI[2]

A67

General purpose input pins.

Pulled high internally on the module.

I 3.3V

PU 10K 3.3V

PU not in PICMG

suggest 10K

GPI[3]

A85

General purpose input pins.

Pulled high internally on the module.

I 3.3V

PU 10K 3.3V

PU not in PICMG

suggest 10K

3.3.15. Power And System Management

Signal

Pin # Description

I/O

PU/PD

Comment

PWRBTN#

B12

Power button to bring system out of S5 (soft off), active on falling edge.

I 3.3VSB

PU 10k

3.3VSB

SYS_RESET#

B49

Reset button input. Active low request for module to reset and reboot. May

be falling edge sensitive. For situations when SYS_RESET# is not able to

reestablish control of the system, PWR_OK or a power cycle may be used.

I 3.3VSB

PU 10k

3.3VSB

CB_RESET#

B50

Reset output from module to Carrier Board. Active low. Issued by module

chipset and may result from a low SYS_RESET# input, a low PWR_OK

input, a VCC_12V power input that falls below the minimum specification, a

watchdog timeout, or may be initiated by the module software.

O 3.3VSB

PWR_OK

B24

Power OK from main power supply. A high value indicates that the power is

good. This signal can be used to hold off Module startup to allow carrier

based FPGAs or other configurable devices time to be programmed.

I 3.3V

TBD by R&D

in CPLD

Should have

weak pull up

SUS_STAT#

B18

Indicates imminent suspend operation; used to notify LPC devices.

O 3.3VSB

SUS_S3#

A15

Indicates system is in Suspend to RAM state. Active-low output. An inverted

copy of SUS_S3# on the carrier board (also known as “PS_ON”) may be

used to enable the non-standby power on a typical ATX power supply.

O 3.3VSB

SUS_S4# A18

Indicates

system is in Suspend to Disk state. Active low output.

O 3.3VSB

SUS_S5#

A24

Indicates system is in Soft Off state.

O 3.3VSB

WAKE0#

B66

PCI Express wake up signal.

I 3.3VSB

PU 10k

3.3VSB