5 timebase, 1 internal sampling clock, 2 external reference clock (pcie-9814p only) – ADLINK PCIe-9814 User Manual

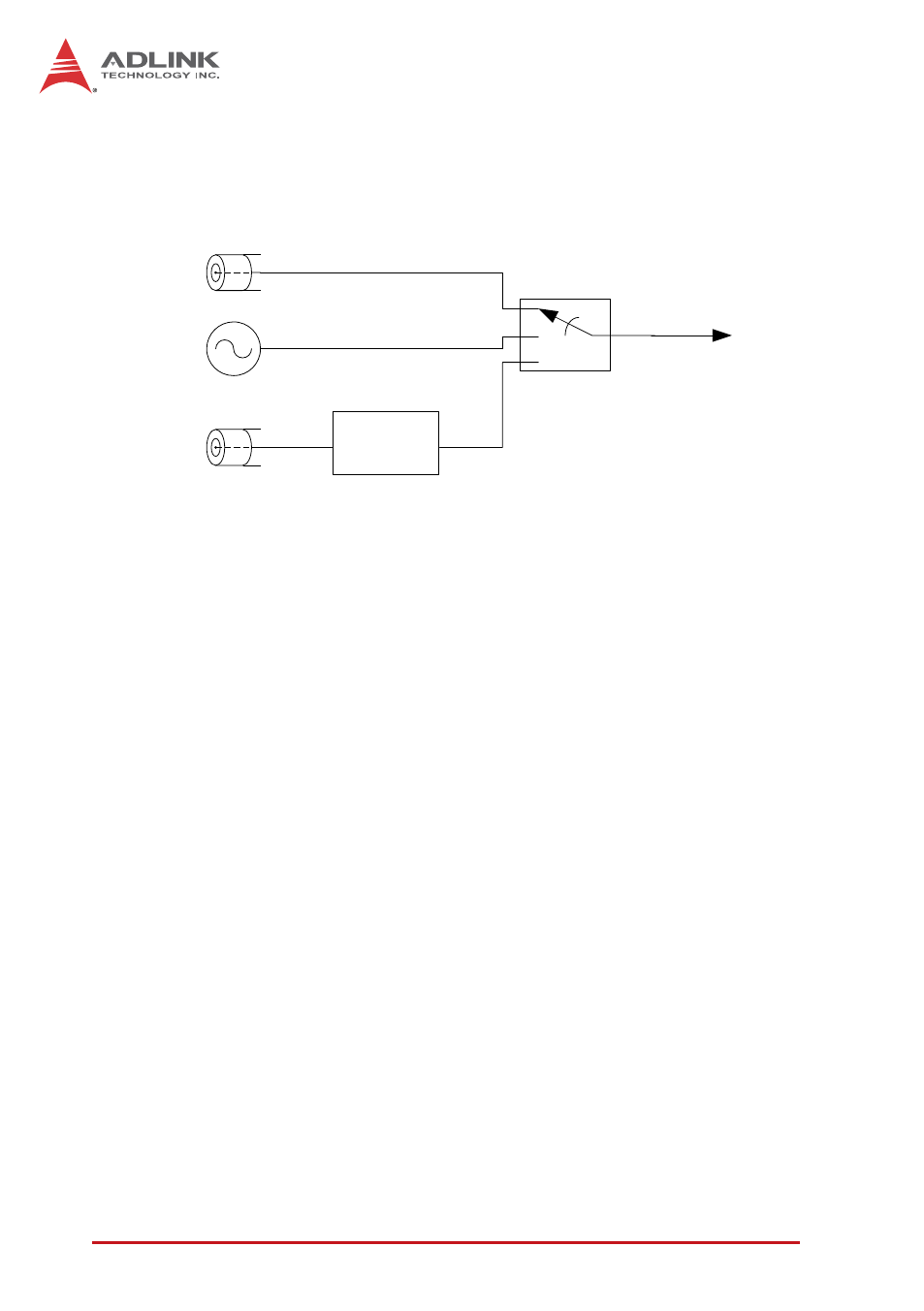

Page 32: 3 external sampling clock, Timebase, Internal sampling clock, External reference clock (pcie-9814p only), External sampling clock, Figure 3-11, Pcie-9814 clock architecture

22

Operations

3.5 Timebase

Figure 3-11: PCIe-9814 Clock Architecture

3.5.1

Internal Sampling Clock

The PCIe-9814 internal 80MHz crystal oscillator acts as a sam-

pling clock for ADC.

3.5.2

External Reference Clock (PCIe-9814P only)

The PCIe-9814P's onboard PLL module allows SDI0 to act as an

external reference clock. Synthesizer input switches to the clock

source at SMB connector SDI0, generating precisely 80MHz clock

for ADC.

3.5.3

External Sampling Clock

The PCIe-9814 can further choose an external clock source as

ADC sampling clock. When an external sampling clock is selected,

the ADC sampling frequency switches to the clock source at SMB

Connector CLK IN, and clock source frequency is available from

20MHz to 80MHz. Be advised that if the frequency of the external

sample clock is changed, the LVDS timebase requires recalibra-

tion.

To do so, call WD-DASK function: WD_AI_Config().

CLK IN

80M Xtal

To ADC

Synthesizer

Board

SDI0