3 dma data transfer, Dma data transfer, Table 3-3: input range midscale values – ADLINK PCIe-9814 User Manual

Page 25

Operations

15

PCIe-9814

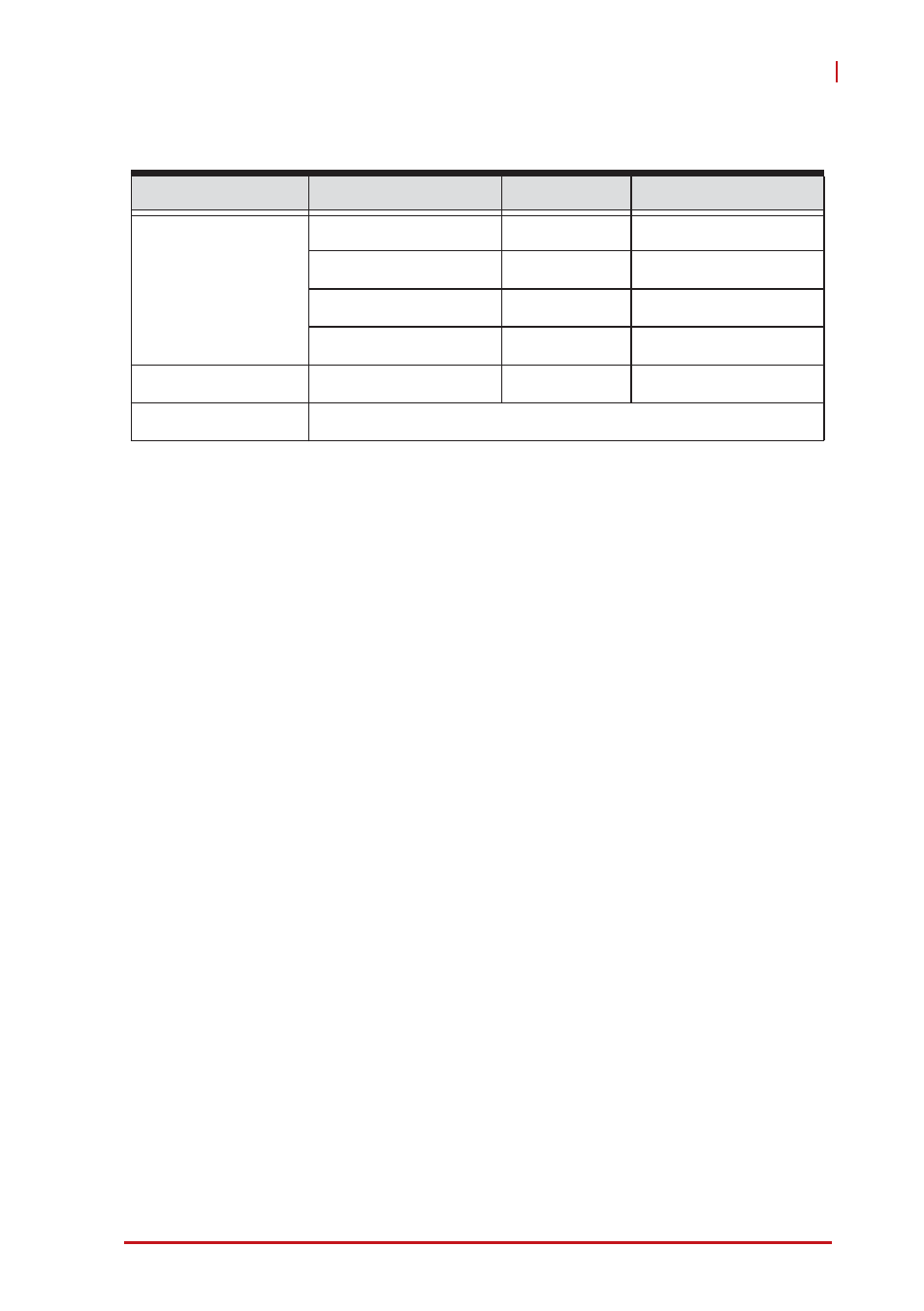

Table 3-3: Input Range Midscale Values

3.2.3

DMA Data Transfer

The PCIe-9814, a PCIe Gen 1 X 4 device, is equipped with a

200MS/s high sampling rate ADC, generating a 640 MByte/

second rate.

To provide efficient data transfer, a PCI bus-mastering DMA is

essential for continuous data streaming, as it helps to achieve full

potential PCI Express bus bandwidth. The bus-mastering control-

ler releases the burden on the host CPU since data is directly

transferred to the host memory without intervention. Once analog

input operation begins, the DMA returns control of the program.

During DMA transfer, the hardware temporarily stores acquired

data in the onboard AD Data FIFO, and then transfers the data to

a user-defined DMA buffer in the computer.

Using a high-level programming library for high speed DMA data

acquisition, the sampling period and the number of conversions

needs simply to be assigned into specified counters. After the AD

trigger condition is met, the data will be transferred to the system

memory by the bus-mastering DMA.

In a multi-user or multi-tasking OS, such as Microsoft Windows,

Linux, or other, it is difficult to allocate a large continuous memory

block. Therefore, the bus controller provides DMA transfer with

scatter-gather function to link non-contiguous memory blocks into

a linked list so users can transfer large amounts of data without

Description

Midscale +1LSB

Midscale

Midscale -1LSB

Bipolar Analog

Input

4.88mV

0V

-4.88mV

2.44mV

0V

-2.44mV

0.488mV

0V

-0.488mV

0.244mV

0V

-0.244mV

Digital Code

0001

0000

FFF0

Comment

SDI bit is assumed to be 0