Table 1-2: pcie-9814 i/o array legend – ADLINK PCIe-9814 User Manual

Page 20

10

Introduction

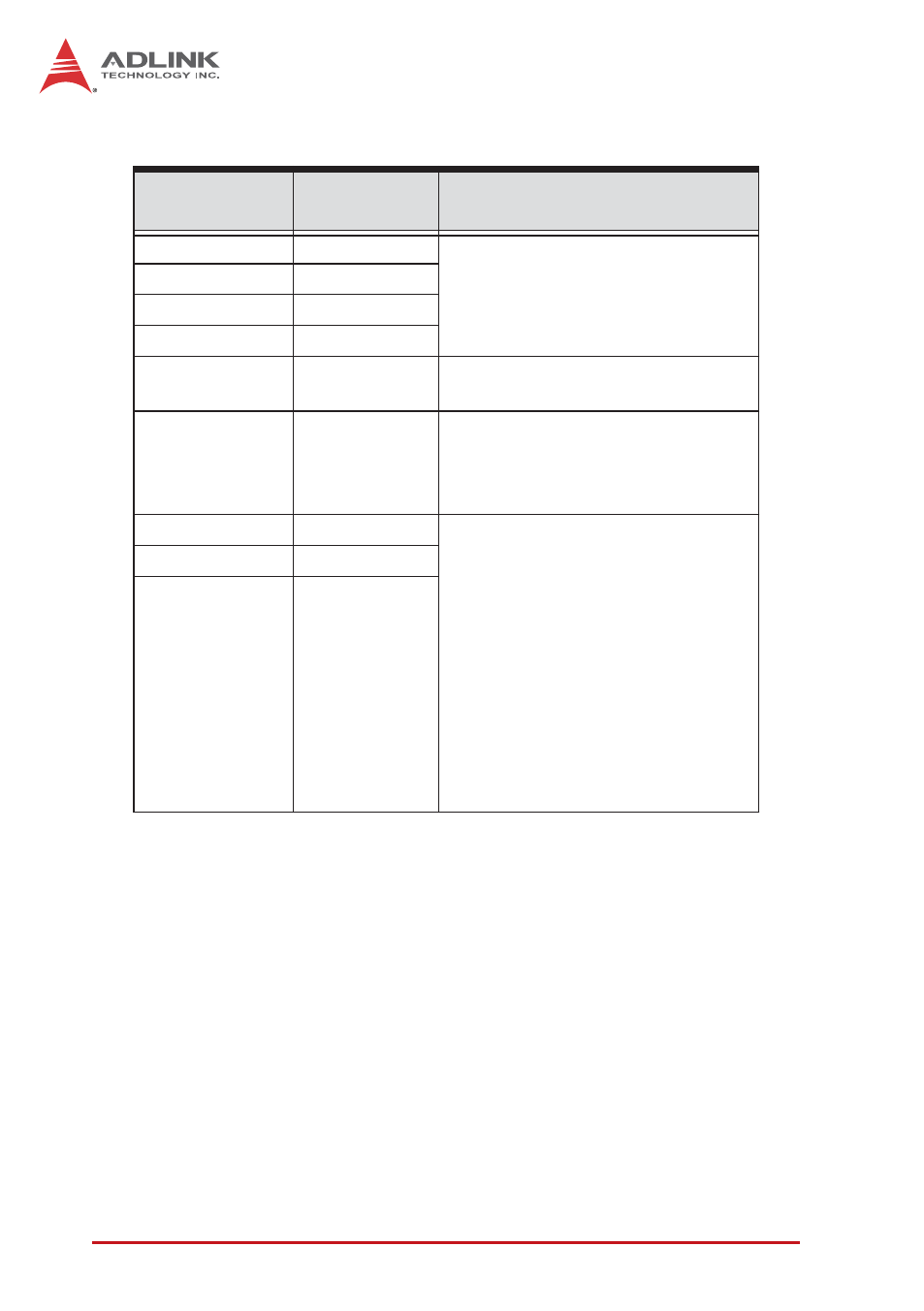

Table 1-2: PCIe-9814 I/O Array Legend

Input

Faceplate

Label

Remark

Analog

CH0

Analog Input Channel

Analog

CH1

Analog

CH2

Analog

CH3

Ext. Clock

CLK

Input for external sample clock to

digitizer

Ext. Digital

Trigger

TRG

External digital trigger input,

receiving trigger signal from

external instrument and initiating

acquisition

Synced Digital

SDI0

3 SDI bits (bit 0:2) and ADC data

are combined into one register and

transferred to host PC by DMA.

Refer to Chapter 3 for detailed data

format.

Optional: For PCIe-9814P (with

PLL module), SDI0 can be used to

receive an external reference 10M

Hz to generate ADC timebase.

Please see Section 3.5.2 External

Reference Clock (PCIe-9814P

only) for more information.

Synced Digital

SDI1

Synced Digital

SDI2

See also other documents in the category ADLINK Hardware:

- USB-1901 (84 pages)

- USB-1210 (54 pages)

- USB-2401 (60 pages)

- USB-7230 (50 pages)

- USB-2405 (56 pages)

- DAQe-2010 (92 pages)

- DAQe-2204 (100 pages)

- DAQe-2213 (94 pages)

- DAQe-2501 (74 pages)

- PXI-2010 (84 pages)

- PXI-2020 (60 pages)

- PXI-2501 (62 pages)

- cPCI-9116 (98 pages)

- ACL-8112 Series (94 pages)

- ACL-8112 Series (92 pages)

- ACL-8112 Series (93 pages)

- ACL-8216 (75 pages)

- ACL-8111 (61 pages)

- PCM-9112+ (10 pages)

- PCM-9112+ (94 pages)

- cPCI-6216V (47 pages)

- ACL-6126 (28 pages)

- ACL-6128A (40 pages)

- PCM-6308V+ (52 pages)

- PCM-6308V+ (4 pages)

- PCI-7444 (82 pages)

- PCI-7434 (48 pages)

- PCI-7234 (56 pages)

- PCI-7260 (66 pages)

- PCI-7258 (38 pages)

- PCI-7256 (48 pages)

- PCI-7250 (48 pages)

- LPCI-7250 (48 pages)

- PCI-7396 (65 pages)

- PCI-7296 (59 pages)

- PCI-8554 (67 pages)

- PCIe-7360 (94 pages)

- PCIe-7350 (86 pages)

- PCIe-7300A (114 pages)

- PCIe-7200 (51 pages)

- PCI-7300A (112 pages)

- PCI-7300A (83 pages)

- PCI-7200 (96 pages)

- cPCI-7300 (82 pages)

- cPCI-7300 (83 pages)